intel Agilex तर्क एरे ब्लकहरू र अनुकूली तर्क मोड्युलहरू

Intel® Agilex™ LAB र ALM ओभरview

तर्क एरे ब्लक (LAB) आधारभूत बिल्डिंग ब्लकहरू मिलेर बनेको छ जसलाई अनुकूलन तर्क मोड्युलहरू (ALMs) भनिन्छ। तपाईं तर्क प्रकार्यहरू, अंकगणित प्रकार्यहरू, र दर्ता कार्यहरू लागू गर्न LABs कन्फिगर गर्न सक्नुहुन्छ।

तपाईंले Intel® Agilex™ यन्त्रहरूमा उपलब्ध LABs को आधा मेमोरी LABs (MLABs) को रूपमा प्रयोग गर्न सक्नुहुन्छ। केहि यन्त्रहरूमा उच्च एमएलएबी अनुपात हुन सक्छ।

Intel Quartus® प्राइम सफ्टवेयर र अन्य समर्थित तेस्रो-पक्ष संश्लेषण उपकरणहरूले स्वचालित रूपमा काउन्टरहरू, adders, subtractors, र अंकगणित प्रकार्यहरू जस्ता सामान्य कार्यहरूको लागि उपयुक्त मोड चयन गर्दछ।

Intel Hyperflex™ कोर आर्किटेक्चर, Intel Agilex Device Overview

Hyper-Registers र Intel Hyperflex™ कोर वास्तुकला बारे थप जानकारी प्रदान गर्दछ। हाइपर-रजस्टरहरू LAB इनपुटहरू र आउटपुटहरूसँग जोडिएका राउटिंग खण्डहरू सहित, कोर कपडामा प्रत्येक इन्टरकनेक्ट राउटिंग खण्डमा उपलब्ध अतिरिक्त दर्ताहरू हुन्।

Intel Hyperflex™ दर्ता

Intel Agilex उपकरण परिवार Intel Hyperflex™ कोर वास्तुकलामा आधारित छ।

Intel Agilex LAB ले Intel Hyperflex रजस्टरहरू र रिटिमिङलाई सहज बनाउन डिजाइन गरिएका अन्य सुविधाहरू समावेश गर्दछ। Intel Hyperflex रजिस्टरहरू ALMs र क्यारी चेनहरूमा उपलब्ध छन्। Intel Agilex ALM जडान विवरण आंकडामा देखाइए अनुसार, Intel Hyperflex रजस्टरहरू सिंक्रोनस क्लियरमा अवस्थित छन् र घडीले पथ ढिलाइ बढाउन वा घटाउन इनपुटहरूलाई सक्षम पार्छ। सबै Intel Hyperflex रेजिस्टरहरू सक्षम गर्न सकिन्छ र रिटाइमिङको समयमा Intel Quartus प्राइम सफ्टवेयरद्वारा नियन्त्रण गरिन्छ।

Intel Agilex LAB र ALM वास्तुकला र सुविधाहरू

निम्न खण्डहरूले Intel Agilex उपकरणहरूको लागि LAB र ALM को वर्णन गर्दछ।

LAB

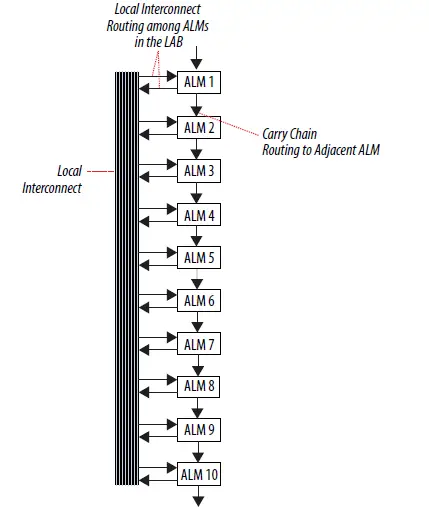

LAB हरू कन्फिगर योग्य तर्क ब्लकहरू हुन् जसमा तर्क स्रोतहरूको समूह हुन्छ। प्रत्येक LAB ले यसको ALM मा ड्राइभिङ नियन्त्रण संकेतहरूको लागि समर्पित तर्क समावेश गर्दछ। MLAB LAB को एक सुपरसेट हो र सबै LAB सुविधाहरू समावेश गर्दछ। Intel Agilex LAB र MLAB स्ट्रक्चर फिगरमा देखाइए अनुसार प्रत्येक LAB मा कुल 10 ALM हरू छन्।

चित्र १।

Intel Agilex LAB संरचना र इन्टरकनेक्ट ओभरview

यो आंकडा एक ओभर देखाउँछview Intel Agilex LAB र MLAB संरचनाको LAB एक अर्कासँग जोडिएको छ।

सम्बन्धित जानकारी

सम्बन्धित जानकारी

एमएलएबी पृष्ठ 6 मा

MLAB

प्रत्येक MLAB ले साधारण डुअल-पोर्ट SRAM को अधिकतम 640 बिट समर्थन गर्दछ। तपाईंले प्रत्येक ALM लाई 32 (गहिराइ) x 2 (चौडाइ) मेमोरी ब्लकको रूपमा एक MLAB मा कन्फिगर गर्न सक्नुहुन्छ, परिणामस्वरूप 32 (गहिराइ) x 20 (चौडाइ) साधारण डुअल-पोर्ट SRAM ब्लकको कन्फिगरेसन हुन्छ।

चित्र १।

Intel Agilex LAB र MLAB संरचना स्थानीय र प्रत्यक्ष लिङ्क इन्टरकनेक्टहरू

स्थानीय र प्रत्यक्ष लिङ्क इन्टरकनेक्टहरू

प्रत्येक LAB ले 60 ALM आउटपुटहरू चलाउन सक्छ। यिनीहरूको एउटा उपसमूहले प्रत्यक्ष रूपमा LAB इनपुटहरू चलाउन सक्छ, तर फरक पङ्क्ति वा स्तम्भमा कुनै पनि जडानले कम्तिमा एउटा सामान्य-उद्देश्य रूटिङ तार प्रयोग गर्नुपर्छ।

स्थानीय इन्टरकनेक्टले ALM इनपुटहरू चलाउँछ। ALM आउटपुटहरू, साथै स्तम्भ र पङ्क्ति इन्टरकनेक्टहरूले स्थानीय इन्टरकनेक्टलाई ड्राइभ गर्दछ।

चित्र १। Intel Agilex LAB स्थानीय र प्रत्यक्ष लिङ्क इन्टरकनेक्ट  क्यारी चेन इन्टरकनेक्टहरू

क्यारी चेन इन्टरकनेक्टहरू

एएलएमहरू बीच एक समर्पित क्यारी चेन मार्ग छ। Intel Agilex उपकरणहरूले कुशल अंकगणितीय कार्यहरूका लागि राउटिङ क्यारी चेनहरूको लागि LABs मा परिष्कृत इन्टरकनेक्ट संरचना समावेश गर्दछ। यी ALM-to-ALM जडानहरूले स्थानीय इन्टरकनेक्टलाई बाइपास गर्छन्।

Intel Hyperflex दर्ताहरू LABs को चेनमा लचिलो रिटिमिङ सक्षम गर्न क्यारी चेनमा थपिन्छन् र Intel Quartus Prime Compiler ले स्वतः एडभान लिन्छ।tagउपयोगिता र कार्यसम्पादन सुधार गर्न यी स्रोतहरूको ई।

चित्र १। क्यारी चेन इन्टरकनेक्टहरू LAB नियन्त्रण संकेतहरू

LAB नियन्त्रण संकेतहरू

प्रत्येक LAB नियन्त्रण ब्लकमा दुईवटा घडी स्रोतहरू छन्, जसले दुईवटा LAB घडीहरू (LABCLK[1:0]) र दुईवटा ढिलाइ भएको LAB घडीहरू (LABCLK_Phi1[1:0]) LAB मा ALM दर्ताहरू र हाइपर-रजस्टरहरू चलाउनको लागि उत्पन्न गर्दछ। LAB ले दुई अद्वितीय घडी सक्षम संकेतहरू, साथै अतिरिक्त स्पष्ट संकेतहरू, ALM दर्ताहरूको लागि समर्थन गर्दछ।

LAB पङ्क्ति घडीहरू [5..0] र LAB स्थानीय इन्टरकनेक्टहरूले LAB-व्यापी नियन्त्रण संकेतहरू उत्पन्न गर्दछ। कम स्क्यू घडी नेटवर्कले पङ्क्ति घडीहरूमा विश्वव्यापी संकेतहरू वितरण गर्दछ [5..0]। मल्टिट्र्याक इन्टरकनेक्टले राउटिंग दक्षताका लागि प्रयोग गरिने विभिन्न लम्बाइ र गतिहरूको निरन्तर, प्रदर्शन-अनुकूलित राउटिंग लाइनहरू समावेश गर्दछ। Intel Quartus प्राइम कम्पाइलरले डिजाइन कार्यसम्पादन सुधार गर्न र यन्त्र स्रोतहरूलाई अनुकूलन गर्नको लागि छिटो इन्टरकनेक्टहरूमा क्रिटिकल डिजाइन पथहरू स्वचालित रूपमा रूट गर्दछ।

तर्क नियन्त्रण खाली गर्नुहोस्

LAB-चौडा संकेतहरूले ALM दर्ताको स्पष्ट संकेतको लागि तर्क नियन्त्रण गर्दछ। ALM दर्ताले सिंक्रोनस र एसिन्क्रोनस क्लियर दुवैलाई सीधा समर्थन गर्दछ। प्रत्येक LAB ले एउटा सिंक्रोनस स्पष्ट संकेत र दुई एसिन्क्रोनस स्पष्ट संकेतहरूलाई समर्थन गर्दछ।

Intel Agilex यन्त्रहरूले यन्त्र-व्यापी रिसेट पिन (DEV_CLRn) प्रदान गर्दछ जसले यन्त्रमा भएका सबै दर्ताहरू रिसेट गर्दछ। तपाईंले संकलन गर्नु अघि Intel Quartus प्राइम सफ्टवेयरमा DEV_CLRn पिन सक्षम गर्न सक्नुहुन्छ। उपकरण-व्यापी रिसेट संकेतले अन्य सबै नियन्त्रण संकेतहरूलाई ओभरराइड गर्दछ।

चित्र १। Intel Agilex LAB-वाइड कन्ट्रोल सिग्नलहरू

ALM

निम्न खण्डहरूले ALM स्रोतहरू, ALM आउटपुट, र ALM अपरेटिङ मोडहरू समावेश गर्दछ।

ALM संसाधनहरू

प्रत्येक ALM ले विभिन्न प्रकारका LUT-आधारित स्रोतहरू समावेश गर्दछ जुन दुई संयोजन अनुकूली LUTs (ALUTs), दुई-बिट पूर्ण एडर, र चार दर्ताहरू बीच विभाजन गर्न सकिन्छ।

दुई संयोजन ALUTs को लागी आठ सम्म इनपुट संग, एक ALM ले दुई प्रकार्यहरु को बिभिन्न संयोजनहरु लागू गर्न सक्छ। यो अनुकूलनताले ALM लाई चार इनपुट LUT आर्किटेक्चरहरूसँग पूर्ण रूपमा पछाडि-कम्प्याटिबल हुन अनुमति दिन्छ। एक ALM ले आठ इनपुट प्रकार्यहरूको एक उपसेट पनि लागू गर्न सक्छ।

एउटा ALM मा चार प्रोग्रामयोग्य दर्ताहरू हुन्छन्। प्रत्येक दर्तामा निम्न पोर्टहरू छन्:

- डाटा मा

- डाटा बाहिर

- सामान्य LAB घडी

- ढिलो LAB घडी

- घडी सक्षम गर्नुहोस्

- सिंक्रोनस स्पष्ट

- एसिन्क्रोनस स्पष्ट

ग्लोबल सिग्नलहरू, सामान्य-उद्देश्य I/O (GPIO) पिनहरू, वा कुनै पनि आन्तरिक तर्कले घडी सक्षम सिग्नल, घडी, र ALM दर्ताको एसिन्क्रोनस वा सिंक्रोनस स्पष्ट नियन्त्रण संकेतहरू चलाउन सक्छ। घडी सक्षम संकेत सिंक्रोनस रिसेट संकेत भन्दा प्राथमिकता छ।

संयोजन प्रकार्यहरूको लागि, दर्ताहरू बाइपास हुन्छन् र लुक-अप तालिका (LUT) र adders को आउटपुट सीधा ALM को आउटपुटहरूमा ड्राइभ गर्दछ। दुई द्रुत आउटपुटहरू 6 LUT आउटपुटहरू र तल्लो 5 LUT आउटपुटहरू आउटपुट मक्सलाई बाइपास गर्न र महत्वपूर्ण पथ समायोजनको लागि अर्को LAB मा जडान गर्न उपलब्ध छन्।

चित्र १। Intel Agilex ALM उच्च-स्तरीय ब्लक रेखाचित्र

ALM आउटपुट

ALM आउटपुट

प्रत्येक ALM मा सामान्य राउटिंग आउटपुटहरूले स्थानीय, पङ्क्ति, र स्तम्भ राउटिंग स्रोतहरू ड्राइभ गर्दछ। छ ALM आउटपुटहरू, दुई द्रुत आउटपुट पथहरू सहित, स्तम्भ, पङ्क्ति, वा प्रत्यक्ष लिङ्क रूटिङ जडानहरू ड्राइभ गर्न सक्छन्।

LUT, adder, वा दर्ता आउटपुटले ALM आउटपुटहरू चलाउन सक्छ। दुबै LUT वा adder र ALM दर्ताले ALM बाट एकैसाथ बाहिर निस्कन सक्छ।

दर्ता प्याकिङले असम्बन्धित दर्ता र संयोजन तर्कलाई एकल ALM मा प्याक गर्न अनुमति दिएर यन्त्र उपयोगमा सुधार गर्दछ। ALM ले LUT वा adder आउटपुटको दर्ता र दर्ता नगरिएका संस्करणहरू पनि निकाल्न सक्छ।

निम्न चित्रले Intel Agilex ALM जडान देखाउँछ। Intel Quartus Prime Resource Property Editor मा, सम्पूर्ण ALM जडान सरलीकृत गरिएको छ। केही रूटिङहरू Intel Quartus प्राइम सफ्टवेयरद्वारा आन्तरिक रूपमा रुट गरिनेछ।

चित्र १। Intel Agilex ALM जडान विवरणहरू ALM सञ्चालन मोडहरू

ALM सञ्चालन मोडहरू

Intel Agilex ALM ले निम्न मोडहरू मध्ये कुनै पनि काम गर्दछ:

- सामान्य मोड

- विस्तारित LUT मोड

- अंकगणित मोड

सामान्य मोड

सामान्य मोडले एउटा Intel Agilex ALM मा दुईवटा प्रकार्यहरू लागू गर्न अनुमति दिन्छ, वा छवटा इनपुटसम्मको एकल प्रकार्य।

LAB स्थानीय इन्टरकनेक्टबाट आठ सम्म डेटा इनपुटहरू संयोजन तर्कमा इनपुटहरू हुन्।

ALM ले पूर्ण रूपमा स्वतन्त्र प्रकार्यहरूको निश्चित संयोजनहरू र साझा इनपुटहरू भएका प्रकार्यहरूको विभिन्न संयोजनहरूलाई समर्थन गर्न सक्छ।

Intel Quartus प्राइम कम्पाइलरले स्वचालित रूपमा LUT मा इनपुटहरू चयन गर्दछ। सामान्य मोड समर्थन दर्ता प्याकिङमा ALMs।

निम्न चित्रले LUT मोडको लागि विभिन्न इनपुट जडानहरूको संयोजन देखाउँछ। तपाईंको डिजाइनमा, Intel Quartus प्राइम सफ्टवेयरले संकलनको क्रममा विभिन्न इनपुट नामहरू तोक्न सक्छ।

चित्र १। सामान्य मोडमा ALM

देखाइएका भन्दा कम इनपुटहरू भएका प्रकार्यहरूको संयोजनहरू पनि समर्थित छन्। पूर्वका लागिample, निम्न संख्या इनपुटहरूको साथ प्रकार्यहरूको संयोजन समर्थित छ।

- १.८.१९ र २.३.२

- १.८.१९ र २.३.२

- १.८.१९ र २.३.२

- १.८.१९ र २.३.२

एउटा ALM मा दुई 5-इनपुट प्रकार्यहरूको प्याकिङको लागि, प्रकार्यहरूमा कम्तिमा दुईवटा साझा इनपुटहरू हुनुपर्छ। सामान्य इनपुटहरू डाटा र डाटाब हुन्। 4-इनपुट प्रकार्यको साथ 5-इनपुट प्रकार्यको संयोजनलाई एउटा साझा इनपुट (कि त dataa वा datab) चाहिन्छ।

कम प्रयोग भएको यन्त्रमा, एउटा ALM मा राख्न सकिने कार्यहरूलाई Intel Quartus प्राइम सफ्टवेयरले उत्कृष्ट सम्भावित कार्यसम्पादन हासिल गर्न छुट्टाछुट्टै ALM मा लागू गर्न सकिन्छ। यन्त्र भर्न थालेपछि, Intel Quartus प्राइम सफ्टवेयरले स्वचालित रूपमा Intel Agilex ALM को पूर्ण क्षमता प्रयोग गर्दछ। Intel Quartus प्राइम कम्पाइलरले स्वचालित रूपमा सामान्य इनपुटहरू प्रयोग गरेर प्रकार्यहरू खोज्छ वा यन्त्र स्रोतहरूको कुशल प्रयोग गर्न एक ALM मा राख्नको लागि पूर्ण रूपमा स्वतन्त्र कार्यहरू खोज्छ। थप रूपमा, तपाईं म्यानुअल रूपमा स्थान असाइनमेन्टहरू सेट गरेर स्रोत प्रयोग नियन्त्रण गर्न सक्नुहुन्छ।

चित्र १। 6-इनपुट LUT मोड प्रकार्य सामान्य मोडमा

चित्र १। 3-इनपुट LUT मोड प्रकार्य सामान्य मोडमा

चित्र १। 3-इनपुट LUT मोड प्रकार्य सामान्य मोडमा

डाटा र डाटा बी दर्ता प्याकिङका लागि उपलब्ध छन्।  तपाइँ निम्न इनपुटहरू प्रयोग गरेर कुनै पनि तीन देखि छ इनपुट प्रकार्य लागू गर्न सक्नुहुन्छ:

तपाइँ निम्न इनपुटहरू प्रयोग गरेर कुनै पनि तीन देखि छ इनपुट प्रकार्य लागू गर्न सक्नुहुन्छ:

- डाटा

- datad0

- datac0

- datac1

- datad1

- dataf

- dataa र datab - जसद्वारा dataa र datab लाई प्रत्येक LUT मा फरक प्रकार्य कार्यान्वयन गर्न लचिलोपन प्रदान गर्न दुबै LUT मा साझा गरिन्छ।

दुबै डाटा र डाटाब इनपुटहरूले दर्ता प्याकिङ सुविधालाई समर्थन गर्दछ। यदि तपाइँले दर्ता प्याकिङ सुविधा सक्षम गर्नुभयो भने, दुबै डेटा र डाटाब इनपुटहरू वा कुनै एक इनपुटले LUT लाई बाइपास गर्छ र प्रयोग गरिएको प्याक गरिएको दर्ता मोडमा निर्भर गर्दै सिधै दर्तामा फिड गर्दछ। Intel Agilex उपकरणहरूका लागि, निम्न प्रकारका प्याक गरिएका दर्ता मोडहरू समर्थित छन्:

- 5-इनपुट LUT 1 प्याक गरिएको दर्ता मार्गको साथ

- 5-इनपुट LUT 2 प्याक गरिएको दर्ता पथहरू

- 3 प्याक गरिएका दर्ता पथहरू सहित दुई 2-इनपुट LUTs

3-इनपुट LUT 2 प्याक गरिएको दर्ता पथहरू सामान्य मोड फिगरमा 3-इनपुट LUT मोड प्रकार्यमा चित्रण गरिएको छ। Intel Agilex उपकरणहरूको लागि, 6-इनपुट LUT मोडले दर्ता प्याकिङ सुविधालाई समर्थन गर्दैन।

विस्तारित LUT मोड

चित्र 11. विस्तारित LUT मोडमा 8-इनपुट प्रकार्यहरू समर्थित

निश्चित 8-इनपुट प्रकार्यहरू सबै LUT इनपुटहरू प्रयोग गरेर एकल ALM मा लागू गर्न सकिन्छ:

- डाटा

- datad0

- datac0

- डाटा

- डाटाब

- datac1

- datad1

- dataf

8-इनपुट विस्तारित LUT मोडमा, प्याक गरिएको दर्ता मोड समर्थित छ, प्रदान गरिएको छ कि प्याक गरिएको दर्ताले 8-इनपुट LUT सँग डाटा वा डाटाब इनपुट साझा गर्दछ।

अंकगणित मोड

अंकगणित मोडमा ALM ले दुई समर्पित पूर्ण एडरहरूका साथ दुई 4-इनपुट LUTs को दुई सेटहरू प्रयोग गर्दछ। समर्पित adders ले LUTs लाई प्रि-एडर तर्क प्रदर्शन गर्न अनुमति दिन्छ। त्यसकारण, प्रत्येक एडरले दुई 4-इनपुट प्रकार्यहरूको आउटपुट थप्न सक्छ।

अंकगणित मोडले घडी सक्षम, काउन्टर सक्षम, सिंक्रोनस माथि र तल नियन्त्रण, थप र घटाउने नियन्त्रण, र सिंक्रोनस क्लियर पनि प्रदान गर्दछ।

स्पष्ट र घडी सक्षम विकल्पहरू LAB- चौडा संकेतहरू हुन् जसले LAB मा सबै दर्ताहरूलाई असर गर्छ। तपाईले व्यक्तिगत रूपमा यी संकेतहरूलाई एक अनुकूली LUT (ALUT) मा दर्ताहरूको प्रत्येक जोडीको लागि अक्षम वा सक्षम गर्न सक्नुहुन्छ। Intel Quartus प्राइम सफ्टवेयरले काउन्टरद्वारा प्रयोग नगरिएका कुनै पनि दर्ताहरूलाई स्वचालित रूपमा अन्य LAB मा राख्छ।

चित्र १। अंकगणित मोडमा Intel Agilex ALM

बोक्ने चेन

बोक्ने चेन

क्यारी चेनले अंकगणित मोडमा समर्पित एडरहरू बीच द्रुत क्यारी प्रकार्य प्रदान गर्दछ।

Intel Agilex उपकरणहरूमा 2-बिट क्यारी चयन सुविधाले ALM सँग क्यारी चेनहरूको प्रसार ढिलाइ विभाजित गर्दछ। क्यारी चेनहरू या त पहिलो ALM वा LAB मा छैटौं ALM मा सुरु गर्न सकिन्छ। अन्तिम क्यारी-आउट सिग्नललाई ALM मा पठाइन्छ, जहाँ यसलाई स्थानीय, पङ्क्ति, वा स्तम्भ इन्टरकनेक्टहरूमा खुवाइन्छ।

Intel Agilex Logic Array Blocks र Adaptive Logic Modules प्रयोगकर्ता गाइडका लागि कागजात संशोधन इतिहास

| कागजात संस्करण | परिवर्तनहरू |

| 2022.05.24 | अद्यावधिक गरिएको चित्र: Intel Agilex ALM उच्च-स्तरीय ब्लक रेखाचित्र। |

| 2019.11.14 | LAB नियन्त्रण सिग्नल खण्डमा विवरण अद्यावधिक गरियो। |

| 2019.10.01 |

|

| 2019.04.02 | प्रारम्भिक रिलीज। |

इंटेल कर्पोरेशन।

सबै अधिकार सुरक्षित। Intel, Intel लोगो, र अन्य Intel मार्कहरू Intel Corporation वा यसको सहायक कम्पनीहरूको ट्रेडमार्क हुन्। Intel ले आफ्नो FPGA र अर्धचालक उत्पादनहरूको प्रदर्शनलाई Intel को मानक वारेन्टी अनुसार हालको विशिष्टताहरूमा वारेन्टी दिन्छ, तर सूचना बिना कुनै पनि समयमा कुनै पनि उत्पादन र सेवाहरूमा परिवर्तन गर्ने अधिकार सुरक्षित गर्दछ। Intel ले यहाँ वर्णन गरिएको कुनै पनि जानकारी, उत्पादन, वा सेवाको आवेदन वा प्रयोगबाट उत्पन्न हुने कुनै जिम्मेवारी वा दायित्व ग्रहण गर्दैन बाहेक Intel द्वारा लिखित रूपमा स्पष्ट रूपमा सहमत भए। Intel ग्राहकहरूलाई कुनै पनि प्रकाशित जानकारीमा भर पर्नु अघि र उत्पादन वा सेवाहरूको लागि अर्डर गर्नु अघि उपकरण विशिष्टताहरूको नवीनतम संस्करण प्राप्त गर्न सल्लाह दिइन्छ।

*अन्य नाम र ब्रान्डहरू अरूको सम्पत्तिको रूपमा दाबी गर्न सकिन्छ।

ISO

००:०५

दर्ता गरियो

कागजातहरू / स्रोतहरू

|

intel Agilex तर्क एरे ब्लकहरू र अनुकूली तर्क मोड्युलहरू [pdf] प्रयोगकर्ता गाइड Agilex Logic Array ब्लकहरू र Adaptive Logic Modules, Agilex, Logic Array Blocks र Adaptive Logic Modules, Array Blocks र Adaptive Logic Modules, Adaptive Logic Modules, Logic Modules |