Intel AN 805 Arria 10 SoC विकास बोर्डमा डिजाइनको हाइरार्किकल आंशिक पुन: कन्फिगरेसन

Intel® Arria® 10 SoC विकास बोर्डको लागि श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन ट्यूटोरियल

यो एप्लिकेसन नोटले साधारण डिजाइनलाई क्रमबद्ध रूपमा आंशिक रूपमा पुन: कन्फिगर गर्न मिल्ने डिजाइनमा रूपान्तरण गर्ने र Intel® Arria® 10 SoC विकास बोर्डमा डिजाइन कार्यान्वयन गर्ने देखाउँछ। हाइरार्किकल आंशिक पुन: कन्फिगरेसन (HPR) एक विशेष प्रकारको आंशिक पुन: कन्फिगरेसन (PR), जहाँ तपाइँ अर्को PR क्षेत्र भित्र PR क्षेत्र समावेश गर्नुहुन्छ। तपाईं बच्चा र अभिभावक विभाजनहरूको लागि धेरै व्यक्तित्वहरू सिर्जना गर्न सक्नुहुन्छ। तपाईंले बच्चा विभाजनहरूलाई तिनीहरूको अभिभावक विभाजनहरूमा नेस्ट गर्नुहुन्छ। बच्चा विभाजन पुन: कन्फिगर गर्दा अभिभावक वा स्थिर क्षेत्रहरूमा सञ्चालनलाई असर गर्दैन। अभिभावक विभाजन पुन: कन्फिगर गर्नाले स्थिर क्षेत्रमा सञ्चालनलाई असर गर्दैन, तर पूर्वनिर्धारित बाल विभाजन व्यक्तित्वहरूसँग अभिभावक क्षेत्रको बाल विभाजनहरू प्रतिस्थापन गर्दछ। यो पद्धति प्रणालीहरूमा प्रभावकारी हुन्छ जहाँ धेरै प्रकार्यहरूले समान FPGA उपकरण स्रोतहरू समय-साझेदारी गर्दछ।

आंशिक पुन: कन्फिगरेसनले फ्लैट डिजाइनमा निम्न प्रगतिहरू प्रदान गर्दछ:

- रन-टाइम डिजाइन पुन: कन्फिगरेसन अनुमति दिन्छ

- डिजाइनको स्केलेबिलिटी बढाउँछ

- प्रणाली डाउनटाइम कम गर्दछ

- डिजाइनमा गतिशील समय-मल्टीप्लेक्सिङ प्रकार्यहरूलाई समर्थन गर्दछ

- बोर्ड स्पेसको कुशल प्रयोग मार्फत लागत र पावर खपत कम गर्दछ

- नोट:

- यस सन्दर्भ डिजाइनको कार्यान्वयनको लागि Intel Quartus® Prime FPGA कार्यान्वयन प्रवाह र प्राथमिक Intel Quartus Prime परियोजनाको ज्ञानको साथ आधारभूत परिचितता आवश्यक छ। files.

सम्बन्धित जानकारी

- Intel Arria 10 SoC विकास किट प्रयोगकर्ता गाइड

- आंशिक पुन: कन्फिगरेसन अवधारणाहरू

- आंशिक पुन: कन्फिगरेसन डिजाइन प्रवाह

- आंशिक पुन: कन्फिगरेसन डिजाइन सिफारिसहरू

- आंशिक पुन: कन्फिगरेसन डिजाइन विचारहरू

सन्दर्भ डिजाइन आवश्यकताहरू

यो सन्दर्भ डिजाइन निम्न आवश्यक छ:

- Intel Quartus प्राइम प्रो संस्करण सफ्टवेयर संस्करण 17.1 डिजाइन कार्यान्वयनको लागि।

- FPGA कार्यान्वयनको लागि Intel Arria 10 SoC विकास किट।

इंटेल कर्पोरेशन। सबै अधिकार सुरक्षित। Intel, Intel लोगो, र अन्य Intel मार्कहरू Intel Corporation वा यसको सहायक कम्पनीहरूको ट्रेडमार्क हुन्। Intel ले आफ्नो FPGA र अर्धचालक उत्पादनहरूको प्रदर्शनलाई Intel को मानक वारेन्टी अनुसार हालको विशिष्टताहरूमा वारेन्टी दिन्छ, तर सूचना बिना कुनै पनि समयमा कुनै पनि उत्पादन र सेवाहरूमा परिवर्तन गर्ने अधिकार सुरक्षित गर्दछ। Intel ले यहाँ वर्णन गरिएको कुनै पनि जानकारी, उत्पादन, वा सेवाको आवेदन वा प्रयोगबाट उत्पन्न हुने कुनै जिम्मेवारी वा दायित्व ग्रहण गर्दैन बाहेक Intel द्वारा लिखित रूपमा स्पष्ट रूपमा सहमत भए। Intel ग्राहकहरूलाई कुनै पनि प्रकाशित जानकारीमा भर पर्नु अघि र उत्पादन वा सेवाहरूको लागि अर्डर गर्नु अघि उपकरण विशिष्टताहरूको नवीनतम संस्करण प्राप्त गर्न सल्लाह दिइन्छ।

- अन्य नाम र ब्रान्डहरू अरूको सम्पत्तिको रूपमा दाबी गर्न सकिन्छ।

सन्दर्भ डिजाइन ओभरview

- यो सन्दर्भ डिजाइन एक 32-बिट काउन्टर समावेश गर्दछ। बोर्ड स्तरमा, डिजाइनले घडीलाई 50MHz स्रोतमा जडान गर्दछ र FPGA मा चार LEDs मा आउटपुट जडान गर्दछ। विशिष्ट अनुक्रममा काउन्टर बिटहरूबाट आउटपुट चयन गर्नाले LEDs लाई एक विशेष फ्रिक्वेन्सीमा झिम्क्याउँछ।

चित्र १। PR विभाजन बिना फ्लैट सन्दर्भ डिजाइन

सन्दर्भ डिजाइन Files

आंशिक पुन: कन्फिगरेसन ट्यूटोरियल निम्न स्थानमा उपलब्ध छ: https://github.com/intel/fpga-partial-reconfig

ट्यूटोरियल डाउनलोड गर्न:

- क्लोन क्लिक गर्नुहोस् वा डाउनलोड गर्नुहोस्।

- जिप डाउनलोड गर्नुहोस् क्लिक गर्नुहोस्। FPGA-partial-config-master.zip अनजिप गर्नुहोस् file.

- सन्दर्भ डिजाइनमा पहुँच गर्न tutorials/a10_soc_devkit_blinking_led_hpr उप-फोल्डरमा नेभिगेट गर्नुहोस्।

फ्ल्याट फोल्डर निम्न समावेश गर्दछ files:

तालिका १. सन्दर्भ डिजाइन Files

| File नाम | विवरण |

| शीर्ष। SV | शीर्ष-स्तर file डिजाइनको समतल कार्यान्वयन समावेश गर्दछ। यो मोड्युलले blinking_led sub-partition र top_counter मोड्युललाई इन्स्ट्यान्टियट गर्छ। |

| top_counter.sv | शीर्ष-स्तर 32-बिट काउन्टर जसले LED[1] लाई सीधा नियन्त्रण गर्दछ। काउन्टरको दर्ता गरिएको आउटपुटले LED[0] लाई नियन्त्रण गर्छ, र Blinking_led मोड्युल मार्फत LED[2] र LED[3] लाई पनि शक्ति दिन्छ। |

| blinking_led.sdc | परियोजनाको लागि समय बाधाहरू परिभाषित गर्दछ। |

| जारी… | |

| File नाम | विवरण |

| blinking_led.SV | यस ट्यूटोरियलमा, तपाईंले यो मोड्युललाई अभिभावक PR विभाजनमा रूपान्तरण गर्नुहुन्छ। मोड्युलले top_counter मोड्युलको दर्ता आउटपुट प्राप्त गर्दछ, जसले LED[2] र LED[3] लाई नियन्त्रण गर्दछ। |

| blinking_led.qpf | इंटेल क्वार्टस प्राइम परियोजना file परियोजना मा सबै संशोधन को सूची समावेश। |

| blinking_led.qsf | इंटेल क्वार्टस प्राइम सेटिंग्स file परियोजनाको लागि असाइनमेन्ट र सेटिङहरू समावेश। |

नोट: hpr फोल्डरले पूर्ण सेट समावेश गर्दछ fileतपाईंले यो अनुप्रयोग नोट प्रयोग गरेर सिर्जना गर्नुभयो। यी सन्दर्भ गर्नुहोस् fileवाकथ्रुको समयमा कुनै पनि बिन्दुमा।

चित्र २. सन्दर्भ डिजाइन Files

सन्दर्भ डिजाइन वाकथ्रु

निम्न चरणहरूले फ्ल्याट डिजाइनमा आंशिक पुन: कन्फिगरेसनको अनुप्रयोगको वर्णन गर्दछ। ट्यूटोरियलले Intel Arria 10 SoC विकास बोर्डको लागि Intel Quartus प्राइम प्रो संस्करण सफ्टवेयर प्रयोग गर्दछ:

- चरण १: पृष्ठ 6 मा सुरु गर्दै

- चरण १: पृष्ठ 6 मा बाल स्तरको उप-मोड्युल सिर्जना गर्नुहोस्

- चरण १: पृष्ठ 7 मा डिजाइन विभाजनहरू सिर्जना गर्दै

- चरण १: पृष्ठ 9 मा PR विभाजनहरूको लागि स्थान र रूटिङ क्षेत्र आवंटित गर्दै

- चरण १: पृष्ठ 10 मा Intel Arria 10 आंशिक पुन: कन्फिगरेसन कन्ट्रोलर आईपी कोर थप्दै

- चरण १: पृष्ठ 13 मा व्यक्तित्वहरू परिभाषित गर्दै

- चरण १: पृष्ठ 15 मा संशोधनहरू सिर्जना गर्दै

- चरण १: पृष्ठ 20 मा श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन प्रवाह स्क्रिप्ट उत्पन्न गर्दै

- चरण १: पृष्ठ 21 मा श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन फ्लो स्क्रिप्ट चलाउँदै

- चरण १: पृष्ठ 22 मा बोर्ड कार्यक्रम

चरण 1: सुरु गर्दै

सन्दर्भ डिजाइन प्रतिलिपि गर्न fileतपाईंको काम गर्ने वातावरणमा s र blinking_led फ्ल्याट डिजाइन कम्पाइल गर्नुहोस्:

- तपाईंको काम गर्ने वातावरणमा डाइरेक्टरी सिर्जना गर्नुहोस्, a10_soc_devkit_blinking_led_hpr।

- डाउनलोड गरिएका ट्यूटोरियलहरू/a10_soc_devkit_blinking_led_hpr/flat उप-फोल्डर निर्देशिकामा प्रतिलिपि गर्नुहोस्, a10_soc_devkit_blinking_led_hpr।

- Intel Quartus Prime Pro Edition सफ्टवेयरमा क्लिक गर्नुहोस् File ➤ परियोजना खोल्नुहोस् र blinking_led.qpf चयन गर्नुहोस्।

- फ्ल्याट डिजाइन कम्पाइल गर्न, क्लिक गर्नुहोस् प्रक्रिया ➤ संकलन सुरु गर्नुहोस्।

चरण २: बाल स्तरको उप-मोड्युल सिर्जना गर्दै

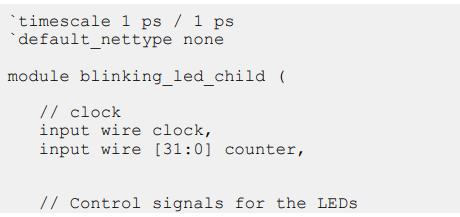

यस फ्ल्याट डिजाइनलाई पदानुक्रमित PR डिजाइनमा रूपान्तरण गर्न, तपाईंले एउटा चाइल्ड सब-मोड्युल (blinking_led_child. SV) सिर्जना गर्नुपर्छ जुन अभिभावक उप-मोड्युल (blinking_led.sv) भित्र नेस्ट गरिएको छ।

- नयाँ डिजाइन सिर्जना गर्नुहोस् file, blinking_led_child.sv, र यसमा कोडका निम्न लाइनहरू थप्नुहोस् file: timescale 1 ps / 1 ps `default_nettype none मोड्युल blinking_led_child ( // घडी इनपुट तार घडी, इनपुट तार [३१:०] काउन्टर, // LEDs को लागि नियन्त्रण संकेतहरू

- blinking_led.sv परिमार्जन गर्नुहोस् file स्थिर क्षेत्रबाट काउन्टरको बिट 23 मा led_two_on जडान गर्न, र blinking_led_child मोड्युल इन्स्ट्यान्टिएट गर्नुहोस्। परिमार्जन पछि, तपाइँको blinking_led.sv file निम्न रूपमा देखा पर्छ:

- सबै डिजाइन परिमार्जन गर्दै files, Processing ➤ Start Compilation मा क्लिक गरेर परियोजना पुन: कम्पाइल गर्नुहोस्

चरण 3: डिजाइन विभाजनहरू सिर्जना गर्दै

तपाईंले आंशिक रूपमा पुन: कन्फिगर गर्न चाहनुभएको प्रत्येक PR क्षेत्रका लागि डिजाइन विभाजनहरू सिर्जना गर्नुपर्छ। तपाईंले आफ्नो डिजाइनमा कुनै पनि स्वतन्त्र विभाजन वा PR क्षेत्रहरू सिर्जना गर्न सक्नुहुन्छ। यस ट्यूटोरियलले u_blinking_led_child र u_blinking_led उदाहरणका लागि दुईवटा डिजाइन विभाजनहरू सिर्जना गर्दछ।

श्रेणीबद्ध आंशिक पुन: कन्फिगरेसनको लागि डिजाइन विभाजनहरू सिर्जना गर्न:

- प्रोजेक्ट नेभिगेटरमा u_blinking_led_child उदाहरणमा दायाँ क्लिक गर्नुहोस् र डिजाइन विभाजन ➤ डिजाइन विभाजनको रूपमा सेट गर्नुहोस् क्लिक गर्नुहोस्। विभाजनको रूपमा सेट गरिएको प्रत्येक उदाहरणको छेउमा एउटा डिजाइन विभाजन प्रतिमा देखिन्छ।

चित्र 3. परियोजना नेभिगेटरबाट डिजाइन विभाजनहरू सिर्जना गर्दै

- विभाजन प्रकार परिभाषित गर्न, हाइरार्की ट्याबमा u_blinking_led_child उदाहरणमा दायाँ-क्लिक गर्नुहोस्, डिजाइन विभाजन ➤ पुन: कन्फिगर योग्य क्लिक गर्नुहोस्। तपाईंले विभाजनको रूपमा उदाहरण सेट गरेपछि मात्र विभाजन प्रकार परिभाषित गर्न सक्नुहुन्छ। डिजाइन विभाजन असाइनमेन्टहरूमा देखिन्छ View डिजाइन विभाजन सञ्झ्यालको ट्याब।

चित्र ४. डिजाइन विभाजन सञ्झ्याल

- नाममा डबल-क्लिक गरेर डिजाइन विभाजन विन्डोमा विभाजन नाम सम्पादन गर्नुहोस्। यो सन्दर्भ डिजाइनको लागि, विभाजनको नाम pr_partition मा पुन: नामाकरण गर्नुहोस्।

नोट: जब तपाइँ विभाजन सिर्जना गर्नुहुन्छ, Intel Quartus प्राइम सफ्टवेयरले स्वचालित रूपमा विभाजन नाम उत्पन्न गर्दछ, उदाहरणको नाम र पदानुक्रम मार्गमा आधारित। यो पूर्वनिर्धारित विभाजन नाम प्रत्येक उदाहरणमा फरक हुन सक्छ। - u_blinking_led उदाहरणमा पुन: कन्फिगर गर्न मिल्ने डिजाइन विभाजनहरू तोक्न चरणहरू 1 र 2 दोहोर्याउनुहोस्। यस विभाजनलाई pr_parent_partition मा पुन: नामाकरण गर्नुहोस्।

blinking_led.qsf मा निम्न कार्यहरू समावेश छन् भनी प्रमाणित गर्नुहोस्, तपाईंको पुन: कन्फिगर गर्न मिल्ने डिजाईन विभाजनहरू अनुरूप:

आंशिक पुन: कन्फिगरेसनको लागि डिजाइन विभाजनहरू सिर्जना गर्नुहोस्

चरण १: PR विभाजनहरूको लागि स्थान र राउटिंग क्षेत्र आवंटित गर्दै

जब तपाइँ आधार संशोधन सिर्जना गर्नुहुन्छ, PR डिजाइन प्रवाहले आरक्षित क्षेत्रमा सम्बन्धित व्यक्ति कोर राख्नको लागि तपाइँको PR विभाजन क्षेत्र आवंटन प्रयोग गर्दछ। तपाईंको आधार संशोधनको लागि यन्त्र फ्लोरप्लानमा PR क्षेत्र पत्ता लगाउन र तोक्न:

- प्रोजेक्ट नेभिगेटरमा u_blinking_led_child उदाहरणमा दायाँ क्लिक गर्नुहोस् र Logic Lock Region ➤ नयाँ Logic Lock Region सिर्जना गर्नुहोस्। क्षेत्र Logic Lock क्षेत्र सञ्झ्यालमा देखिन्छ।

- तपाईंको प्लेसमेन्ट क्षेत्रले blinking_led_child तर्कलाई संलग्न गर्नुपर्छ। चिप प्लानरमा नोड पत्ता लगाएर प्लेसमेन्ट क्षेत्र चयन गर्नुहोस्। प्रोजेक्ट नेभिगेटरमा u_blinking_led_child क्षेत्रको नाममा दायाँ क्लिक गर्नुहोस् र Locate Node ➤ Locate in Chip Planner मा क्लिक गर्नुहोस्।

चित्र 5. blinking_led को लागी चिप प्लानर नोड स्थान

- Logic Lock Regions सञ्झ्यालमा, Origin स्तम्भमा प्लेसमेन्ट क्षेत्र निर्देशांकहरू निर्दिष्ट गर्नुहोस्। उत्पत्ति क्षेत्रको तल्लो-बायाँ कुनासँग मेल खान्छ। पूर्वका लागिample, (X1 Y1) को रूपमा (69 10) समन्वयको साथ प्लेसमेन्ट क्षेत्र सेट गर्न, X69_Y10 को रूपमा उत्पत्ति निर्दिष्ट गर्नुहोस्। Intel Quartus प्राइम सफ्टवेयरले तपाईले निर्दिष्ट गर्नुभएको उचाइ र चौडाइको आधारमा प्लेसमेन्ट क्षेत्रका लागि (X2 Y2) समन्वयहरू (शीर्ष-दायाँ) स्वचालित रूपमा गणना गर्दछ।

नोट: यस ट्यूटोरियलले (X1 Y1) समन्वयहरू - (69 10), र प्लेसमेन्ट क्षेत्रका लागि 20 को उचाइ र चौडाइ प्रयोग गर्दछ। प्लेसमेन्ट क्षेत्रको लागि कुनै पनि मान परिभाषित गर्नुहोस्, बशर्ते कि क्षेत्रले blinking_led_child तर्कलाई समेट्छ। - आरक्षित र कोर-मात्र विकल्पहरू सक्षम गर्नुहोस्।

- रूटिङ क्षेत्र विकल्पमा डबल क्लिक गर्नुहोस्। Logic Lock Routing Region Settings संवाद बाकस देखिन्छ।

- राउटिंग प्रकारको लागि विस्तारसँग फिक्स्ड चयन गर्नुहोस्। यो विकल्प चयन गर्दा स्वतः 1 को विस्तार लम्बाइ तोकिन्छ।

नोट: इन्जिनले विभिन्न व्यक्तिहरूलाई रुट गर्दा फिटरलाई थप लचिलोपन प्रदान गर्न राउटिङ क्षेत्र प्लेसमेन्ट क्षेत्रभन्दा ठूलो हुनुपर्छ। - u_blinking_led उदाहरणका लागि चरण 1 -6 दोहोर्याउनुहोस्। अभिभावक-स्तर प्लेसमेन्ट u_blinking_led उदाहरणका लागि चरण 1 -6 दोहोर्याउनुहोस्। अभिभावक-स्तरको प्लेसमेन्ट क्षेत्रले अभिभावक-स्तर तर्क प्लेसमेन्टको लागि पर्याप्त ठाउँको अनुमति दिँदा सम्बन्धित बाल-स्तर प्लेसमेन्ट र रूटिङ क्षेत्रहरू पूर्ण रूपमा संलग्न गर्नुपर्छ। यस ट्यूटोरियलले (X1 Y1) निर्देशांकहरू प्रयोग गर्दछ - (66 7), 47 को उचाइ, र u_blinking_led उदाहरणको प्लेसमेन्ट क्षेत्रको लागि 26 को चौडाइ।

चित्र 6. तर्क लक क्षेत्र सञ्झ्याल

blinking_led.qsf मा निम्न असाइनमेन्टहरू छन् भनी प्रमाणित गर्नुहोस्, तपाईंको फ्लोर प्लानिङसँग सम्बन्धित:

- फ्लोरप्लान आंशिक पुन: कन्फिगरेसन डिजाइन

- विस्तारित रूपमा आंशिक पुन: कन्फिगरेसन कार्यान्वयन गर्दै

चरण 5: Intel Arria 10 आंशिक पुन: कन्फिगरेसन कन्ट्रोलर आईपी कोर थप्दै

- PR विभाजन पुन: कन्फिगर गर्न Intel Arria 10 आंशिक पुन: कन्फिगरेसन नियन्त्रक IP कोर प्रयोग गर्नुहोस्। यो आईपी कोर J प्रयोग गर्दछTAG PR विभाजन पुन: कन्फिगर गर्न। तपाईंको इंटेल क्वार्टस प्राइम प्रोजेक्टमा Intel Arria 10 आंशिक पुन: कन्फिगरेसन कन्ट्रोलर आईपी कोर थप्न:

- IP क्याटलगमा आंशिक पुन: कन्फिगरेसन टाइप गर्नुहोस्।

- IP प्यारामिटर सम्पादक प्रो विन्डो सुरु गर्न, आईपी लाइब्रेरीबाट Intel Arria 10 आंशिक पुन: कन्फिगरेसन कन्ट्रोलर IP कोर चयन गर्नुहोस्, र थप्नुहोस् क्लिक गर्नुहोस्।

- नयाँ आईपी भेरियन्ट संवाद बक्समा, pr_ip को रूपमा टाइप गर्नुहोस् file नाम र सिर्जना क्लिक गर्नुहोस्। pr_ip को लागि पूर्वनिर्धारित प्यारामिटराइजेसन प्रयोग गर्नुहोस्। सुनिश्चित गर्नुहोस् कि सक्षम JTAG डिबग मोड र सक्षम फ्रिज इन्टरफेस विकल्पहरू सक्रिय छन्, र Avalon-MM दास इन्टरफेस सक्षम गर्नुहोस् विकल्प बन्द गरिएको छ।

चित्र 7. Intel Arria 10 आंशिक पुन: कन्फिगरेसन नियन्त्रक आईपी कोर प्यारामिटरहरू

- समाप्त क्लिक गर्नुहोस्, र प्रणाली उत्पन्न नगरी प्यारामिटर सम्पादकबाट बाहिर निस्कनुहोस्। इंटेल क्वार्टस प्राइम सफ्टवेयरले pr_ip.ip IP भिन्नता सिर्जना गर्दछ file, र थप्छ file blinking_led परियोजनामा।

नोट:

- यदि तपाइँ pr_ip.ip प्रतिलिपि गर्दै हुनुहुन्छ file hpr फोल्डरबाट, blinking_led.qsf लाई म्यानुअल रूपमा सम्पादन गर्नुहोस् file निम्न रेखा समावेश गर्न: set_global_assignment -name IP_FILE pr_ip.ip

- IP_ राख्नुहोस्FILE SDC_ पछि असाइनमेन्टFILE असाइनमेन्ट (jtag.sdc र blinking_led.sdc) तपाईंको blinking_led.qsf मा file। यो क्रमले आंशिक पुन: कन्फिगरेसन IP कोरको उपयुक्त अवरोध सुनिश्चित गर्दछ।

नोट: घडीहरू पत्ता लगाउन, SDC file PR IP को लागि IP कोरले प्रयोग गर्ने घडीहरू सिर्जना गर्ने कुनै पनि SDC पालना गर्नुपर्छ। तपाईंले .ip लाई सुनिश्चित गरेर यो अर्डरलाई सहज बनाउनुहुन्छ file PR IP कोरको लागि कुनै पनि .ip पछि आउँछ files वा SDC files QSF मा यी घडीहरू सिर्जना गर्न प्रयोग गरिन्छ file तपाईंको इंटेल क्वार्टस प्राइम प्रोजेक्ट संशोधनको लागि। थप जानकारीको लागि, आंशिक पुन: कन्फिगरेसन आईपी कोर प्रयोगकर्ता गाइडमा समय बाधाहरू खण्ड हेर्नुहोस्।

सम्बन्धित जानकारी

- आंशिक पुन: कन्फिगरेसन आईपी समाधान प्रयोगकर्ता गाइड

- आंशिक पुन: कन्फिगरेसन क्षेत्र नियन्त्रक आईपी कोरमा जानकारीको लागि।

- आंशिक पुन: कन्फिगरेसन आईपी कोर प्रयोगकर्ता गाइड

- समय सीमा बारे जानकारी को लागी।

शीर्ष-स्तर डिजाइन अपडेट गर्दै

Top.SV अपडेट गर्न file PR_IP उदाहरण संग:

- शीर्ष-स्तरको डिजाइनमा PR_IP उदाहरण थप्न, शीर्षमा निम्न कोड ब्लक अनकमेन्ट गर्नुहोस्।SV file:

- पुन: कन्फिगरेसनको क्रममा आउटपुट पोर्टहरूलाई तर्क १ मा बल गर्न, PR_IP बाट फ्रिज नियन्त्रण संकेत आउटपुट प्रयोग गर्नुहोस्। यद्यपि, बाल विभाजनलाई PR प्रोग्रामिङ गर्दा अभिभावक PR विभाजनबाट LED झिम्किरहेको देख्न, फ्रिज नियन्त्रण संकेतले led_two_on बन्द गर्दैन। सुनिश्चित गर्नुहोस् कि pr_led_two_on प्रत्यक्ष छ

- पूर्वनिर्धारित अभिभावक व्यक्तित्व (blinking_led) को एक उदाहरण असाइन गर्न, शीर्ष अपडेट गर्नुहोस्।SV file कोड को निम्न ब्लक संग:

चित्र 8. आंशिक पुन: कन्फिगरेसन आईपी कोर एकीकरण

चरण 6: व्यक्तित्वहरू परिभाषित गर्दै

यस सन्दर्भ डिजाइनले अभिभावक र बाल PR विभाजनहरूको लागि पाँच अलग-अलग व्यक्तिहरूलाई परिभाषित गर्दछ। परिभाषित गर्न र तपाईंको परियोजनामा व्यक्तित्वहरू समावेश गर्न:

- चार SystemVerilog सिर्जना गर्नुहोस् files, blinking_led_child.sv, blinking_led_child_slow.sv, blinking_led_child_empty.sv, र blinking_led_slow.sv पाँच व्यक्तिहरूको लागि तपाईंको कार्य निर्देशिकामा।

नोट: यदि तपाइँ SystemVerilog सिर्जना गर्नुहुन्छ fileइंटेल क्वार्टस प्राइम टेक्स्ट एडिटरबाट, एड असक्षम पार्नुहोस् file हालको परियोजना विकल्पमा, बचत गर्दा files.

तालिका २. सन्दर्भ डिजाइन व्यक्तित्वहरू

| File नाम | विवरण | कोड |

| blinking_led_child.sv | बाल-स्तर डिजाइनको लागि पूर्वनिर्धारित व्यक्तित्व |

`टाइमस्केल १ पीएस / १ पीएस `default_nettype none मोड्युल blinking_led_child ( // घडी इनपुट तार घडी, इनपुट तार [३१:०] काउन्टर,

// LEDs आउटपुट तार led_three_on को लागि नियन्त्रण संकेतहरू

); localparam COUNTER_TAP = 23; reg led_three_on_r;

led_three_on = led_three_on_r असाइन गर्नुहोस्; सधैं_ff @(पोजेज घडी) सुरु हुन्छ led_three_on_r <= counter[COUNTER_TAP]; अन्त्य

एन्डमोड्युल |

| जारी… | ||

| File नाम | विवरण | कोड |

| blinking_led_child_slow.sv | द

LED_THREE ढिलो झिम्काउँछ |

`टाइमस्केल १ पीएस / १ पीएस `पूर्वनिर्धारित_नेटप्रकार कुनै पनि होइन

मोड्युल blinking_led_child_slow (

// घडी इनपुट तार घडी, इनपुट तार [३१:०] काउन्टर,

// LEDs आउटपुट तार led_three_on को लागि नियन्त्रण संकेतहरू );

localparam COUNTER_TAP = 27; reg led_three_on_r;

led_three_on = led_three_on_r असाइन गर्नुहोस्; सधैं_ff @(पोजेज घडी) सुरु हुन्छ led_three_on_r <= counter[COUNTER_TAP]; अन्त्य

एन्डमोड्युल |

| blinking_led_child_empty.sv | द

LED_THREE जारी रहन्छ |

`टाइमस्केल १ पीएस / १ पीएस `पूर्वनिर्धारित_नेटप्रकार कुनै पनि होइन

मोड्युल blinking_led_child_empty (

// घडी इनपुट तार घडी, इनपुट तार [३१:०] काउन्टर,

// LEDs आउटपुट तार led_three_on को लागि नियन्त्रण संकेतहरू

);

// LED सक्रिय कम छ led_three_on = 1'b0 असाइन गर्नुहोस्;

एन्डमोड्युल |

| blinking_led_slow.sv | LED_TWO

ढिलो झिम्काउँछ। |

`टाइमस्केल १ पीएस / १ पीएस `default_nettype none मोड्युल blinking_led_slow( // घडी इनपुट तार घडी, इनपुट तार [३१:०] काउन्टर,

// LEDs आउटपुट तार led_two_on को लागि नियन्त्रण संकेतहरू, आउटपुट तार led_three_on

);

localparam COUNTER_TAP = 27; reg led_two_on_r; असाइन गर्नुहोस् led_two_on = led_two_on_r;

// काउन्टर: सधैं_ff @(पोजेज घडी) सुरु हुन्छ led_two_on_r <= counter[COUNTER_TAP]; अन्त्य

ब्लिंकिङ_लेड_बाल u_blinking_led_child( .led_three_on (led_three_on), काउन्टर (काउन्टर), घडी (घडी) |

| File नाम | विवरण | कोड |

| ;ndmodule |

चरण 3: पृष्ठ 7 मा डिजाइन विभाजनहरू सिर्जना गर्दै

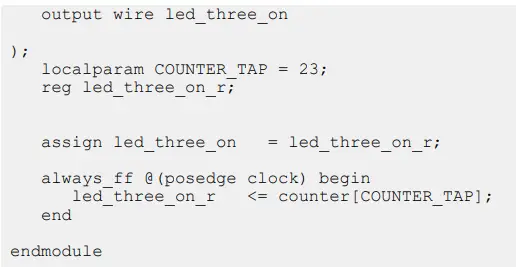

चरण 7: संशोधनहरू सिर्जना गर्दै

PR डिजाइन प्रवाहले Intel Quartus प्राइम सफ्टवेयरमा परियोजना संशोधन सुविधा प्रयोग गर्दछ। तपाईंको प्रारम्भिक डिजाइन आधार संशोधन हो, जहाँ तपाईंले FPGA मा स्थिर क्षेत्र सीमाहरू र पुन: कन्फिगर योग्य क्षेत्रहरू परिभाषित गर्नुहुन्छ। आधार संशोधनबाट, तपाइँ बहुविध संशोधनहरू सिर्जना गर्नुहुन्छ। यी संशोधनहरूले PR क्षेत्रहरूका लागि विभिन्न कार्यान्वयनहरू समावेश गर्दछ। यद्यपि, सबै PR कार्यान्वयन संशोधनहरूले आधार संशोधनबाट उही शीर्ष-स्तर प्लेसमेन्ट र रूटिङ परिणामहरू प्रयोग गर्छन्। PR डिजाइन कम्पाइल गर्न, तपाईंले प्रत्येक व्यक्तित्वको लागि PR कार्यान्वयन संशोधन र संश्लेषण संशोधन सिर्जना गर्नुपर्छ। यस सन्दर्भ डिजाइनमा, आधार संशोधन (blinking_led) को अतिरिक्त, तीन बाल-स्तर व्यक्तित्वहरू र दुई अभिभावक-स्तर व्यक्तित्वहरूमा पाँच अलग-अलग संश्लेषण संशोधन र पाँच अलग-अलग कार्यान्वयन संशोधनहरू छन्:

तालिका 3. दुई-अभिभावक व्यक्तिहरू र तीन-बच्चा व्यक्तिहरूका लागि संशोधनहरू

| संश्लेषण संशोधन | कार्यान्वयन संशोधन |

| blinking_led_parent, blinking_led_default | blinking_led_pr_alpha |

| blinking_led_parent, blinking_led_child_slow | blinking_led_pr_bravo |

| blinking_led_parent, blinking_led_child_empty | blinking_led_pr_charlie |

| blinking_led_parent_slow, blinking_led_child_slow | blinking_led_pr_delta |

| blinking_led_parent_slow, blinking_led_child_empty | blinking_led_pr_emma |

कार्यान्वयन संशोधनहरू सिर्जना गर्दै

PR कार्यान्वयन संशोधनहरू सिर्जना गर्न:

- संशोधन संवाद बाकस खोल्नको लागि, परियोजना ➤ संशोधनहरूमा क्लिक गर्नुहोस्।

- नयाँ संशोधन सिर्जना गर्न, डबल-क्लिक गर्नुहोस् < >।

- संशोधन नाम blinking_led_pr_alpha को रूपमा निर्दिष्ट गर्नुहोस् र संशोधनको आधारमा blinking_led चयन गर्नुहोस्।

- हालको संशोधन विकल्पको रूपमा सेट अक्षम गर्नुहोस् र ठीक क्लिक गर्नुहोस्।

- त्यसैगरी, ब्लिंकिङ_लेड_पीआर_ब्राभो, ब्लिङ्किङ_लेड_पीआर_चार्ली, ब्लिङ्किङ_लेड_पीआर_डेल्टा, र ब्लिङ्किङ_लेड_पीआर_एम्मा संशोधनहरू सिर्जना गर्नुहोस्, ब्लिङ्किङ_लेड संशोधनको आधारमा।

नोट: माथिका संशोधनहरूलाई हालको संशोधनको रूपमा सेट नगर्नुहोस्।

चित्र 9. संशोधनहरू सिर्जना गर्दै

संश्लेषण-मात्र संशोधनहरू सिर्जना गर्दै

व्यक्तिहरूका लागि संश्लेषण-मात्र संशोधनहरू सिर्जना गर्न, तपाईंले शीर्ष-स्तर इकाई र सम्बन्धित SystemVerilog असाइन गर्नुपर्छ। file प्रत्येक व्यक्तिको लागि:

- Intel Quartus प्राइम सफ्टवेयरमा, Project ➤ Revisions मा क्लिक गर्नुहोस्।

- blinking_led_default संशोधन blinking_led संशोधनमा आधारित बनाउनुहोस्। यो संशोधनलाई हालको संशोधनको रूपमा सेट नगर्नुहोस्।

- blinking_led_default.qsf परिमार्जन गर्नुहोस् file निम्न कार्यहरू समावेश गर्न:

set_global_assignment -नाम TOP_LEVEL_ENTITY blinking_led_child

set_global_assignment -नाम SYSTEMVERILOG_FILE - त्यसैगरी, ब्लिङ्किङ_लेड_चाइल्ड_स्लो, ब्लिङ्किङ_लेड_चाइल्ड_एम्पटी, ब्लिङ्किङ_लेड_प्यारेन्ट र ब्लिङ्किङ_लेड_प्यारेन्ट_स्लो रिभिजनहरू ब्लिङ्किङ_लेड रिभिजनमा आधारित बनाउनुहोस्। यी संशोधनहरूलाई हालको संशोधनको रूपमा सेट नगर्नुहोस्।

- blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, र blinking_led_parent_slow.qsf अपडेट गर्नुहोस् files तिनीहरूको संगत संग

TOP_LEVEL_ENTITY र SYSTEMVERILOG_FILE असाइनमेन्टहरू:

- संश्लेषण त्रुटिहरूबाट बच्न, संश्लेषण संशोधन सुनिश्चित गर्नुहोस् fileबाल विभाजनका लागि s मा कुनै पनि डिजाइन विभाजन, पिन असाइनमेन्ट, वा तर्क लक समावेश छैन।

क्षेत्रीय कार्यहरू। साथै, संश्लेषण संशोधन fileअभिभावक विभाजनहरूको लागि s मा सम्बन्धित बाल विभाजनहरूको लागि डिजाइन विभाजन कार्यहरू मात्र समावेश हुनुपर्छ। blinking_led_default.qsf, blinking_led_child_slow.qsf, blinking_led_child_empty.qsf, blinking_led_parent.qsf, र blinking_led_parent_slow.pdf मा यी असाइनमेन्टहरू हटाउनुहोस्। files

- blinking_led_parent.qsf र blinking_led_parent_slow.qsf मा निम्न असाइनमेन्टहरू समावेश गर्नुहोस् files:

- blinking_led.qpf प्रमाणित गर्नुहोस् file निम्न संशोधनहरू समावेश गर्दछ, कुनै विशेष क्रममा:

- नोट: यदि तपाइँ संशोधन प्रतिलिपि गर्दै हुनुहुन्छ भने files hpr फोल्डरबाट, म्यानुअल रूपमा blinking_led.qpf अद्यावधिक गर्नुहोस् file कोड को माथिको लाइनहरु संग।

संशोधन प्रकार निर्दिष्ट गर्दै

तपाईंले आफ्नो प्रत्येक संशोधनको लागि संशोधन प्रकार तोक्नुपर्छ। त्यहाँ तीनवटा संशोधन प्रकारहरू छन्:

- आंशिक पुन: कन्फिगरेसन - आधार

- आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण

- आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन

- निम्न तालिकाले प्रत्येक संशोधनको लागि संशोधन-प्रकार असाइनमेन्टहरू सूचीबद्ध गर्दछ:

तालिका 4. संशोधन प्रकारहरू

| संशोधन नाम | संशोधन प्रकार |

| blinking_led.qsf | आंशिक पुन: कन्फिगरेसन - आधार |

| blinking_led_default.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण |

| blinking_led_child_empty.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण |

| blinking_led_child_slow.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण |

| blinking_led_parent.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण |

| blinking_led_parent_slow.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व संश्लेषण |

| blinking_led_pr_alpha.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन |

| blinking_led_pr_bravo.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन |

| blinking_led_pr_charlie.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन |

| blinking_led_pr_delta.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन |

| blinking_led_pr_emma.qsf | आंशिक पुन: कन्फिगरेसन - व्यक्तित्व कार्यान्वयन |

- परियोजना ➤ संशोधनहरूमा क्लिक गर्नुहोस्। संशोधन संवाद बाकस देखिन्छ।

- संशोधन नाम स्तम्भमा blinking_led चयन गर्नुहोस्, र वर्तमान सेट गर्नुहोस् क्लिक गर्नुहोस्।

- लागू गर्नुहोस् क्लिक गर्नुहोस्। blinking_led संशोधन खुल्छ।

- blinking_led को लागि संशोधन प्रकार सेट गर्न, Assignments ➤ Settings ➤ General मा क्लिक गर्नुहोस्।

- आंशिक पुन: कन्फिगरेसन - आधारको रूपमा संशोधन प्रकार चयन गर्नुहोस्।

- त्यसै गरी, माथिको तालिकामा सूचीबद्ध अन्य दस संशोधनहरूको लागि संशोधन प्रकारहरू सेट गर्नुहोस्।

- नोट: तपाईंले संशोधन प्रकार नियुक्त गर्नु अघि प्रत्येक संशोधनलाई हालको संशोधनको रूपमा सेट गर्नुपर्छ। प्रमाणित गर्नुहोस् कि प्रत्येक .qsf file निम्न असाइनमेन्ट समावेश:

- नोट: कुनै पनि फिटर-विशिष्ट सेटिङहरू थप्नुहोस् जुन तपाइँ PR कार्यान्वयन कम्पाइलमा व्यक्तित्व कार्यान्वयन संशोधनहरूमा प्रयोग गर्न चाहनुहुन्छ। फिटर-विशिष्ट सेटिङहरूले व्यक्तित्वको फिटलाई असर गर्छ, तर आयातित स्थिर क्षेत्रलाई असर गर्दैन। तपाईले व्यक्तिगत व्यक्तित्व संश्लेषण संशोधनहरूमा कुनै पनि संश्लेषण-विशिष्ट सेटिङहरू थप्न सक्नुहुन्छ।

व्यक्तिहरूको लागि संशोधनहरू सिर्जना गर्नुहोस्

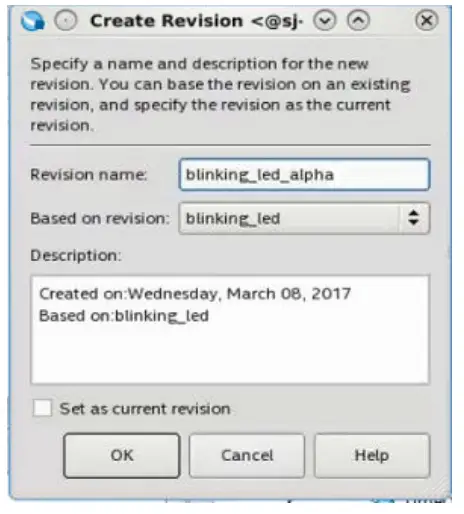

चरण १: श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन प्रवाह स्क्रिप्ट उत्पन्न गर्दै

श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन प्रवाह स्क्रिप्ट उत्पन्न गर्न:

- Intel Quartus प्राइम कमाण्ड शेलबाट, निम्न आदेश चलाएर फ्लो टेम्प्लेट सिर्जना गर्नुहोस्:

- इंटेल क्वार्टस प्राइमले a10_hier_partial_reconfig/flow.tcl उत्पन्न गर्दछ file.

- उत्पन्न a10_hier_partial_reconfig/setup.tcl.ex को पुन: नामाकरण गर्नुहोस्ampa10_hier_partial_reconfig/setup.tcl मा जानुहोस्, र तपाईंको आंशिक पुन: कन्फिगरेसन परियोजना विवरणहरू निर्दिष्ट गर्न स्क्रिप्ट परिमार्जन गर्नुहोस्:

a. परियोजनाको नाम परिभाषित गर्न, निम्न रेखा अद्यावधिक गर्नुहोस्: b. आधार संशोधन परिभाषित गर्न, निम्न रेखा अद्यावधिक गर्नुहोस्:

b. आधार संशोधन परिभाषित गर्न, निम्न रेखा अद्यावधिक गर्नुहोस्:

- प्रत्येक आंशिक पुन: कन्फिगरेसन कार्यान्वयन संशोधनहरू परिभाषित गर्न, PR विभाजन नामहरू र संशोधनहरू लागू गर्ने स्रोत संशोधनको साथ, निम्न रेखाहरू अद्यावधिक गर्नुहोस्:

नोट: सबै संशोधन परियोजनाहरू blinking_led.qpf को रूपमा एउटै निर्देशिकामा हुनुपर्छ। अन्यथा, तदनुसार प्रवाह स्क्रिप्ट अपडेट गर्नुहोस्।

चरण १: पदानुक्रमिक आंशिक पुन: कन्फिगरेसन प्रवाह लिपि चलाउँदै

श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन प्रवाह स्क्रिप्ट चलाउन:

- क्लिक गर्नुहोस् उपकरण ➤ Tcl स्क्रिप्ट। Tcl स्क्रिप्ट संवाद बाकस देखिन्छ।

- प्रोजेक्टमा थप्नुहोस् क्लिक गर्नुहोस्, ब्राउज गर्नुहोस् र a10_hier_partial_reconfig/flow.tcl चयन गर्नुहोस्।

- पुस्तकालय फलकमा a10_hier_partial_reconfig/flow.tcl चयन गर्नुहोस्, र चलाउनुहोस् क्लिक गर्नुहोस्।

यो लिपिले तीन व्यक्तिहरूको लागि संश्लेषण चलाउँछ। इंटेल क्वार्टस प्राइमले SRAM वस्तु उत्पन्न गर्दछ File (.sof), आंशिक-मास्क गरिएको SRAM वस्तु File (.pmsf), र एक कच्चा बाइनरी File (.rbf) प्रत्येक व्यक्तिको लागि।

नोट: इंटेल क्वार्टस प्राइम कमाण्ड शेलबाट स्क्रिप्ट चलाउन, निम्न आदेश टाइप गर्नुहोस्:

- आंशिक पुन: कन्फिगरेसन डिजाइन कम्पाइल गर्नुहोस्

- आंशिक पुन: कन्फिगरेसन फ्लो स्क्रिप्ट प्रयोग गर्दै

- आंशिक पुन: कन्फिगरेसन प्रवाह स्क्रिप्ट कन्फिगर गर्दै

- प्रोग्रामिङ उत्पन्न गर्नुहोस् Files

चरण १: बोर्ड कार्यक्रम गर्दै

तपाईंले सुरु गर्नु अघि:

- Intel Arria 10 SoC विकास बोर्डमा बिजुली आपूर्ति जडान गर्नुहोस्।

- तपाईंको PC USB पोर्ट र विकास बोर्डमा USB ब्लास्टर पोर्ट बीच USB ब्लास्टर केबल जडान गर्नुहोस्।

Intel Arria 10 SoC विकास बोर्डमा डिजाइन चलाउनको लागि:

- Intel Quartus प्राइम सफ्टवेयर खोल्नुहोस् र Tools ➤ Programmer मा क्लिक गर्नुहोस्।

- प्रोग्रामरमा, हार्डवेयर सेटअपमा क्लिक गर्नुहोस् र USB-ब्लास्टर चयन गर्नुहोस्।

- स्वत: पत्ता लगाउन क्लिक गर्नुहोस् र उपकरण चयन गर्नुहोस्, 10AS066N3।

- ठीक क्लिक गर्नुहोस्। इंटेल क्वार्टस प्राइम सफ्टवेयरले बोर्डमा तीनवटा FPGA चिपहरूसँग प्रोग्रामर पत्ता लगाउँछ र अद्यावधिक गर्दछ।

- 10AS066N3 उपकरण चयन गर्नुहोस्, परिवर्तन क्लिक गर्नुहोस् File र blinking_led_pr_alpha.sof लोड गर्नुहोस् file.

- blinking_led_pr_alpha.sof को लागि कार्यक्रम/कन्फिगर सक्षम गर्नुहोस् file.

- सुरुमा क्लिक गर्नुहोस् र प्रगति पट्टी 100% पुग्नको लागि पर्खनुहोस्।

- मूल फ्ल्याट डिजाइन जस्तै फ्रिक्वेन्सीमा झिम्किरहेको बोर्डमा एलईडीहरू हेर्नुहोस्।

- बाल PR क्षेत्र मात्र प्रोग्राम गर्न, blinking_led_pr_alpha.sof मा दायाँ क्लिक गर्नुहोस् file Programmer मा र Add PR Programming मा क्लिक गर्नुहोस् File.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf चयन गर्नुहोस् file.

- blinking_led_pr_alpha.sof को लागि कार्यक्रम/कन्फिगर असक्षम गर्नुहोस् file.

- blinking_led_pr_bravo.pr_parent_partition.pr_partition.rbf को लागि कार्यक्रम/कन्फिगर सक्षम गर्नुहोस् file र सुरु क्लिक गर्नुहोस्। बोर्डमा, LED[0] र LED[1] लाई निरन्तर झिम्किरहेको अवलोकन गर्नुहोस्। जब प्रगति पट्टी 100% पुग्छ, LED[2] उही दरमा झिम्काउँछ, र LED[3] बिस्तारै झिम्काउँछ।

- अभिभावक र बच्चा PR क्षेत्र दुवै कार्यक्रम गर्न, .rbf मा दायाँ क्लिक गर्नुहोस् file प्रोग्रामरमा र PR प्रोग्रामिङ परिवर्तन गर्नुहोस् क्लिक गर्नुहोस् File.

- blinking_led_pr_delta.pr_parent_partition.rbf चयन गर्नुहोस् file.

- सुरु क्लिक गर्नुहोस्। बोर्डमा, LED[0] र LED[1] झिम्काउन जारी रहेको अवलोकन गर्नुहोस्। जब प्रगति पट्टी 100% पुग्छ, दुबै LED [2] र LED [3] ढिलो झिम्काउँछन्।

- केवल बाल PR क्षेत्र, वा दुवै अभिभावक र बाल PR क्षेत्रहरू एकै साथ गतिशील रूपमा पुन: कार्यक्रम गर्न माथिका चरणहरू दोहोर्याउनुहोस्।

चित्र 10. Intel Arria 10 SoC विकास बोर्ड प्रोग्रामिङ

अवस्थित व्यक्तित्व परिमार्जन गर्दै

- तपाईले अवस्थित व्यक्तित्व परिवर्तन गर्न सक्नुहुन्छ, आधार संशोधन पूर्ण रूपमा कम्पाइल गरेपछि पनि।

- पूर्वका लागिample, blinking_led_child_slow व्यक्तित्वलाई अझ ढिलो झिम्काउनको लागि:

- blinking_led_child_slow.sv मा file, COUNTER_TAP प्यारामिटर 27 देखि 28 सम्म परिमार्जन गर्नुहोस्।

- यो व्यक्तित्व पुन: संश्लेषण र पुन: लागू गर्न, तपाईंले परिवर्तनबाट प्रभावित सबै संश्लेषण-मात्र संशोधन र कार्यान्वयन संशोधनहरू पुन: कम्पाइल गर्नुपर्छ। निम्न रेखाहरू समावेश गर्न setup.tcl लिपि परिमार्जन गर्नुहोस्:

नोट: blinking_led_pr_delta संशोधनको लागि pr_parent_parition परिभाषित गर्दा, तपाईंले कार्यान्वयनको लागि त्यो व्यक्तित्वको अन्तिम स्न्यापसट आयात गर्नुहुन्छ। नतिजाको रूपमा, अभिभावक विभाजन तर्कको कार्यान्वयन समान रहन्छ, सम्बन्धित बाल विभाजनलाई परिमार्जन र कार्यान्वयन गर्दा।

नोट: blinking_led_pr_delta संशोधनको लागि pr_parent_parition परिभाषित गर्दा, तपाईंले कार्यान्वयनको लागि त्यो व्यक्तित्वको अन्तिम स्न्यापसट आयात गर्नुहुन्छ। नतिजाको रूपमा, अभिभावक विभाजन तर्कको कार्यान्वयन समान रहन्छ, सम्बन्धित बाल विभाजनलाई परिमार्जन र कार्यान्वयन गर्दा। यो आदेशले blinking_led_child_slow संश्लेषण संशोधन पुन: संश्लेषण गर्दछ, र त्यसपछि blinking_led_pr_bravo प्रयोग गरेर PR कार्यान्वयन कम्पाइल चलाउँछ।

यो आदेशले blinking_led_child_slow संश्लेषण संशोधन पुन: संश्लेषण गर्दछ, र त्यसपछि blinking_led_pr_bravo प्रयोग गरेर PR कार्यान्वयन कम्पाइल चलाउँछ। - संश्लेषण-मात्र संशोधनहरूको संकलन गर्न, निम्न आदेश चलाउनुहोस्: यो आदेशले आधार संशोधन पुन: कम्पाइल गर्दैन।

- कार्यान्वयन संशोधनहरूको संकलन गर्न, निम्न आदेश चलाउनुहोस्:

- यो आदेशले आधार संशोधन पुन: कम्पाइल गर्दैन।

- चरण 10 मा दिइएका चरणहरू पालना गर्नुहोस्: परिणामित RBF कार्यक्रम गर्न पृष्ठ 22 मा बोर्डलाई प्रोग्रामिङ गर्नुहोस् file FPGA मा।

नोट: प्रत्येक संशोधनको लागि सम्पूर्ण प्रवाह चलाउनबाट बच्न, setup.tcl स्क्रिप्टमा संश्लेषण-मात्र संशोधन र कार्यान्वयन संशोधनहरू परिभाषित गर्नुहोस्, र स्क्रिप्ट चलाउनुहोस्।

डिजाइनमा नयाँ व्यक्तित्व थप्दै

तपाईंको आधार संशोधनहरू पूर्ण रूपमा कम्पाइल गरेपछि, तपाईं अझै पनि नयाँ व्यक्तित्वहरू थप्न सक्नुहुन्छ र व्यक्तिगत रूपमा यी व्यक्तिहरूलाई कम्पाइल गर्न सक्नुहुन्छ।

पूर्वका लागिample, blinking_led_parent_slow को लागि नयाँ बाल व्यक्तित्व परिभाषित गर्न, जसले led_three लाई निष्क्रिय पार्छ:

- blinking_led_child_empty.sv लाई blinking_led_chdild_off.sv मा प्रतिलिपि गर्नुहोस्।

- blinking_led_child_off.sv मा file, असाइनमेन्ट परिमार्जन गर्नुहोस्, led_three_on = 1'b0 असाइन गर्नुहोस्; led_three_on = 1'b1; असाइन गर्न। तपाईंले मोड्युलको नामलाई blinking_led_child_empty बाट blinking_led_child_off मा परिवर्तन गरेको सुनिश्चित गर्नुहोस्।

- पृष्ठ 16 मा संश्लेषण-मात्र संशोधनहरू सिर्जना गर्ने चरणहरू पछ्याएर, blinking_led_child_off, नयाँ संश्लेषण संशोधन सिर्जना गर्नुहोस्।

नोट: blinking_led_child_off संशोधनले blinking_led_child_off.sv प्रयोग गर्नुपर्छ file. - पृष्ठ 15 मा कार्यान्वयन संशोधनहरू सिर्जना गर्ने चरणहरू पछ्याएर, blinking_led_pr_foxtrot, नयाँ कार्यान्वयन संशोधन सिर्जना गर्नुहोस्।

- a10_hier_partial_reconfig/setup.tcl अपडेट गर्नुहोस् file नयाँ PR कार्यान्वयन परिभाषित गर्न:

- निम्न आदेश चलाएर यो नयाँ संश्लेषण र कार्यान्वयन संशोधन कम्पाइल गर्नुहोस्:

Intel Arria 10 उपकरणहरूको लागि श्रेणीबद्ध आंशिक पुन: कन्फिगरेसनमा पूर्ण जानकारीको लागि, Intel Quartus प्राइम प्रो संस्करण ह्यान्डबुकको भोल्युम 1 मा आंशिक पुन: कन्फिगरेसन डिजाइन सिर्जना गर्ने सन्दर्भ गर्नुहोस्।

सम्बन्धित जानकारी

- आंशिक पुन: कन्फिगरेसन डिजाइन सिर्जना गर्दै

- आंशिक पुन: कन्फिगरेसन अनलाइन प्रशिक्षण

कागजात संशोधन इतिहास

तालिका २.. कागजात संशोधन इतिहास

| कागजात संस्करण | सफ्टवेयर संस्करण | परिवर्तनहरू |

| 2017.11.06 | 17.1.0 | • अद्यावधिक गरियो सन्दर्भ डिजाइन आवश्यकताहरू सफ्टवेयर संस्करण संग खण्ड

• अद्यावधिक गरियो PR विभाजन बिना फ्लैट सन्दर्भ डिजाइन डिजाइन ब्लक परिवर्तन संग चित्र • अद्यावधिक गरियो सन्दर्भ डिजाइन Files जानकारी सहितको तालिका Top_counter.sv मोड्युल • अद्यावधिक गरियो आंशिक पुन: कन्फिगरेसन आईपी कोर एकीकरण डिजाइन ब्लक परिवर्तन संग चित्र • तथ्याङ्कहरू अद्यावधिक गरियो - डिजाइन विभाजन विन्डो र तर्क लक क्षेत्र विन्डो नयाँ GUI प्रतिबिम्बित गर्न • File नाम परिवर्तन • पाठ सम्पादनहरू |

| 2017.05.08 | 17.0.0 | कागजातको प्रारम्भिक विमोचन |

कागजातहरू / स्रोतहरू

|

Intel AN 805 Arria 10 SoC विकास बोर्डमा डिजाइनको हाइरार्किकल आंशिक पुन: कन्फिगरेसन [pdf] प्रयोगकर्ता गाइड Arria 805 SoC विकास बोर्डमा डिजाइनको AN 10 पदानुक्रमिक आंशिक पुन: कन्फिगरेसन, AN 805, Arria 10 SoC विकास बोर्डमा डिजाइनको श्रेणीबद्ध आंशिक पुन: कन्फिगरेसन, Arria 10 SoC विकास बोर्डमा डिजाइनको पुन: कन्फिगरेसन, Arria 10 SoC विकास बोर्ड, 10 SoC विकास बोर्ड |