AN3468

एक प्रकार 1/2 802.3 वा HDBaseT प्रकार 3 संचालित डिजाइन गर्दै

PD702x0 र PD701x0 ICs प्रयोग गरेर यन्त्रको अगाडि-अन्त

परिचय

यो एप्लिकेसन नोटले IEEE® 802.3af, IEEE 802.3at, HDBaseT (PoH), र युनिभर्सल पावर ओभर इथरनेट (UPoE) अनुप्रयोगहरूको लागि माइक्रोचिपको अगाडिको परिवार प्रयोग गरेर पावर ओभर इथरनेट (PoE) पावर्ड डिभाइस (PD) प्रणाली डिजाइन गर्न दिशानिर्देशहरू प्रदान गर्दछ। -अन्त पीडी एकीकृत सर्किट। निम्न तालिकाले माइक्रोचिप पीडी उत्पादनहरू प्रस्तावहरू सूचीबद्ध गर्दछ।

तालिका 1. माइक्रोचिप संचालित उपकरण उत्पादन प्रस्तावहरू

| भाग | टाइप गर्नुहोस् | प्याकेज | IEEE® 802.3af |

IEEE 802.3at |

HDBaseT (PoH) |

UPoE |

| PD70100 | अगाडिको छेउ | 3 मिमी × 4 मिमी 12L DFN | x | - | - | - |

| PD70101 | अगाडि छेउ + PWM | 5 मिमी × 5 मिमी 32L QFN | x | - | - | - |

| PD70200 | अगाडिको छेउ | 3 मिमी × 4 मिमी 12L DFN | x | x | - | - |

| PD70201 | अगाडि छेउ + PWM | 5 मिमी × 5 मिमी 32L QFN | x | x | - | - |

| PD70210 | अगाडिको छेउ | 4 मिमी × 5 मिमी 16L DFN | x | x | x | x |

| PD70210A | अगाडिको छेउ | 4 मिमी × 5 मिमी 16L DFN | x | x | x | x |

| PD70210AL | अगाडिको छेउ | 5 मिमी × 7 मिमी 38L QFN | x | x | x | x |

| PD70211 | अगाडि छेउ + PWM | 6 मिमी × 6 मिमी 36L QFN | x | x | x | x |

| PD70224 | आदर्श डायोड पुल | 6 मिमी × 8 मिमी 40L QFN | x | x | x | x |

माइक्रोचिपले स्ट्यान्डअलोन फ्रन्ट-एन्ड PD उपकरणहरू प्रदान गर्दछ जसलाई उच्च PoE भोल्युम रूपान्तरण गर्न बाह्य PWM IC आवश्यक पर्दछ।tage तल विनियमित आपूर्ति भोल्युममाtage अनुप्रयोग द्वारा प्रयोग गरिएको। थप रूपमा, माइक्रोचिपले PD उपकरणहरू प्रदान गर्दछ जसले उत्पादन प्याकेजमा फ्रन्ट-एन्ड PD र PWM लाई एकीकृत गर्दछ। यस एप्लिकेसन नोटको दायरा भनेको माइक्रोचिप फ्रन्ट-एन्ड-मात्र उत्पादनहरू (PD701x0 र PD702x0) प्रयोग गरेर PoE PD फ्रन्टको डिजाइन वर्णन गर्नु हो। यस कागजातमा माइक्रोचिपको PD उत्पादनहरूको मुख्य विशेषताहरू र कार्यहरूको विवरण पनि समावेश छ, संक्षिप्तमाview PoE कार्यक्षमता, मापदण्ड र PoE PD डिजाइनको लागि प्रमुख प्राविधिक विचारहरू।

फ्रन्ट-एन्ड PD उत्पादनहरूले आवश्यक पत्ता लगाउने, वर्गीकरण, पावर-अप प्रकार्यहरू, र सूचीबद्ध मापदण्डहरू अनुरूप सञ्चालन हालको स्तरहरू प्रदान गर्दछ।

माइक्रोचिपले PoE PD अनुप्रयोगहरूको लागि पूरक उत्पादन प्रदान गर्दछ, PD70224 Ideal Diode Bridge, जुन इनपुट ध्रुवता सुरक्षाको लागि डुअल डायोड ब्रिजहरूको कम घाटा विकल्प हो।

माइक्रोचिपले पूर्ण सन्दर्भ डिजाइन प्याकेजहरू र मूल्याङ्कन बोर्डहरू (EVBs) प्रदान गर्दछ। यी डिजाइन प्याकेजहरू, उपकरण डेटा पानाहरू, वा अनुप्रयोग नोटहरूमा पहुँचको लागि, कृपया आफ्नो स्थानीय माइक्रोचिप ग्राहक संलग्नता प्रबन्धकसँग परामर्श गर्नुहोस् वा हाम्रो भ्रमण गर्नुहोस्। webसाइट मा www.microchip.com/poe.

प्राविधिक सहयोगको लागि, आफ्नो स्थानीय इम्बेडेड समाधान इन्जिनियरहरूसँग परामर्श गर्नुहोस् वा जानुहोस् microchipsupport.force.com/s/.

माइक्रोचिप PoE फ्रन्ट-एन्ड PD कन्ट्रोलर प्रमुख विशेषताहरू

निम्न सबै माइक्रोचिप PoE को सामान्य विशेषताहरू छन्

- PD नियन्त्रकहरू।

- PD पत्ता लगाउने हस्ताक्षर

- प्रोग्रामेबल PD वर्गीकरण हस्ताक्षर

- एकीकृत अलगाव स्विच

- पावर अन हुँदा २४.९ k पत्ता लगाउने सिग्नेचर रेसिस्टर विच्छेदन, पावर बचतको लागि

- इनरश वर्तमान सीमा (सफ्ट स्टार्ट)

- DC-DC कन्भर्टरहरूको लागि एकीकृत 10.5V स्टार्ट-अप आपूर्ति आउटपुट

- अधिभार संरक्षण

- DC-DC बल्क क्यापेसिटरको लागि आन्तरिक डिस्चार्ज सर्किटरी

- चौडा तापमान सञ्चालन दायरा 40 ° C देखि 85 ° C

- अन-चिप थर्मल संरक्षण

निम्न तालिकाले PoE PD नियन्त्रकहरूमा फरक फरक हुने सुविधाहरू सूचीबद्ध गर्दछ।

तालिका 2. माइक्रोचिप PoE फ्रन्ट-एन्ड PD कन्ट्रोलर प्रमुख विशेषताहरू

| भाग नम्बर | आईसी प्रकार | मानकहरू | अधिकतम शक्ति (W) |

अधिकतम वर्तमान (A) |

अधिकतम प्रतिरोध (Ω) |

झण्डा १ | WA प्राथमिकता पिन १ |

VAUX |

| PD70100 | अगाडिको अन्त्य | आईईईई 802.3०२.af एएफ | 15.4 | 0.45 | 0.6 | PGOOD | छैन | हो |

| PD70200 | अगाडिको अन्त्य | आईईईई 802.3०२.af एएफ IEEE 802.3at |

47 | 1.123 | 0.6 | PGOOD मा २-घटना |

छैन | हो |

| PD70210A/AL | अगाडिको अन्त्य | आईईईई 802.3०२.af एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.3 | AT 4P_AT HD 4P_HD २/३ घटना |

हो | हो |

| PD70210 | अगाडिको अन्त्य | आईईईई 802.3०२.af एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.3 | AT 4P_AT HD 4P_HD PGOOD २/३ घटना |

छैन | हो |

| PD70224 | आदर्श डायोड पुल |

आईईईई 802.3०२.af एएफ IEEE 802.3at PoH UPoE |

95 | 2 | 0.76 | N/A | N/A | N/A |

- विस्तृत विवरणहरूको लागि, 4. सामान्य सञ्चालन सिद्धान्त हेर्नुहोस्।

a AT - AT झण्डा

b 4P_AT — 4-जोडा AT झण्डा

ग HD—HDBaseT झण्डा

d 4P_HD—4-जोडा HDBaseT

e PGOOD - शक्ति राम्रो झण्डा - WA प्राथमिकता पिनले भित्ता एडाप्टर कार्यक्षमताको समर्थन नियन्त्रण गर्दछ र बाह्य DC स्रोतबाट लोडमा शक्ति आपूर्ति गर्न सहायक आपूर्ति प्राथमिकता लागू गर्दछ।

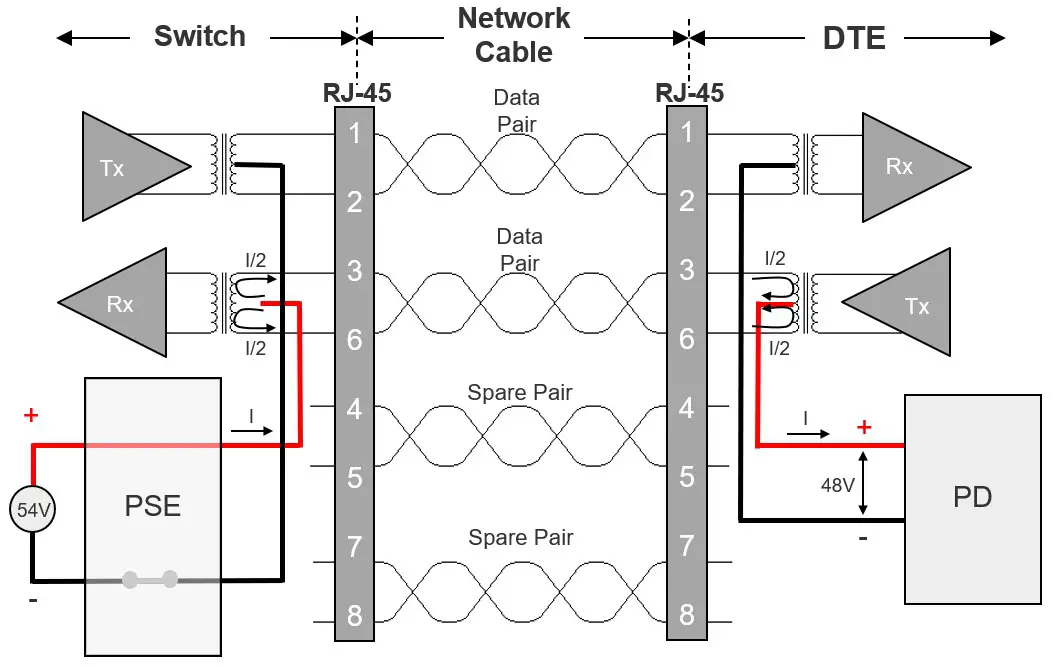

PoE ओभरview

PoE ले पावर सोर्स इक्विपमेन्ट (PSE), एक इथरनेट वा नेटवर्क केबल (सामान्यतया पूर्वाधारमा समावेश गरिएको) 100 मिटरको अधिकतम लम्बाइ भएको, र एक पावरेड डिभाइस (PD) समावेश गर्दछ जसले डेटा र पावर दुबै स्वीकार गर्दछ। इथरनेट केबलको पावर इन्टरफेस (PI)। PI सामान्यतया आठ पिन RJ45 प्रकारको कनेक्टर हो। PSE सामान्यतया इथरनेट स्विच वा Midspan मा रहन्छ। PD लाई कहिलेकाहीं डाटा टर्मिनल इक्विपमेन्ट (DTE) भनिन्छ। निम्न तथ्याङ्कहरूले यस व्यवस्थाको रेखाचित्र देखाउँछन्।

चित्र १-१। डेटामा दुई-जोडा शक्ति - वैकल्पिक ए

चित्र १-२। दुई जोडी पावर ओभर स्पेयर - वैकल्पिक B

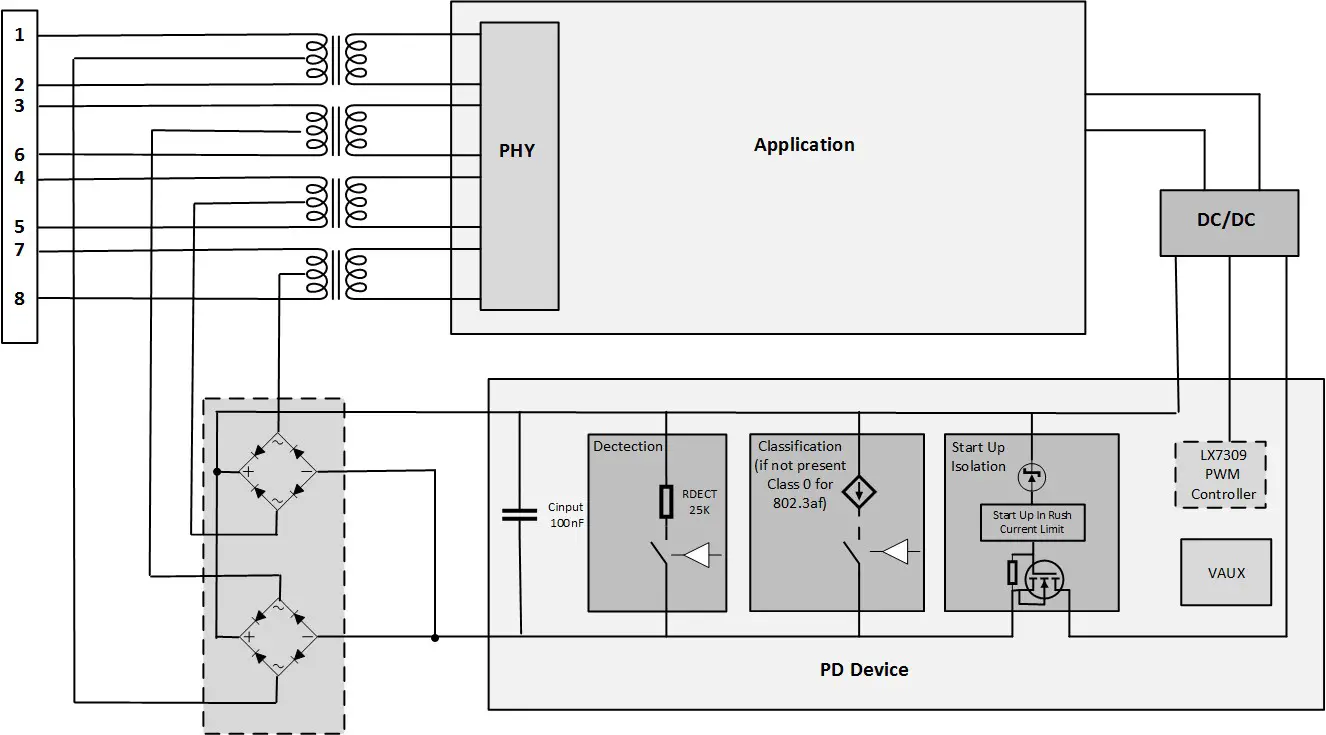

चित्र १-३। आधारभूत PD ब्लक रेखाचित्र

PD ले निम्न कार्यहरू प्रदान गर्दछ।

- ध्रुवता संरक्षण - भोल्युमtagPI मा ध्रुवता मापदण्ड द्वारा ग्यारेन्टी छैन। त्यसकारण, PD इनपुटमा सही ध्रुवता सुनिश्चित गर्न डायोड ब्रिज प्रयोग गरिन्छ। अनुकूलित पावर हानि र PCB क्षेत्र को लागी, माइक्रोचिप PD70224 आदर्श डायोड ब्रिज प्रयोग गर्नुहोस्। मानक डायोड पुलहरू पनि प्रयोग गर्न सकिन्छ।

- पत्ता लगाउने - पत्ता लगाउनको लागि हस्ताक्षर प्रदान गर्दछ।

- वर्गीकरण - वर्गीकरण हस्ताक्षर को लागी हस्ताक्षर प्रदान गर्दछ।

- स्टार्ट-अप - पत्ता लगाउन र वर्गीकरण पछि, एक नियन्त्रित पावर अनुप्रयोग प्रदान गर्दछ।

- Isolation-PoE डोमेनमा पृथ्वीको जमीन र प्रयोगकर्ता पहुँचयोग्य भागहरूबाट 1500 VAC अलगाव हुनुपर्छ। यो पृथक DC/DC कनवर्टर मार्फत यो अलगाव प्रदान गर्न सिफारिस गरिएको छ। गैर-पृथक डिजाइनहरूसँग, अन्तिम अनुप्रयोगले यो अलगाव प्रदान गर्नुपर्छ। त्यहाँ एक धारणा छ कि गैर-पृथक डिजाइनले लागत बचत गर्छ, तर वास्तवमा यो आवश्यक रूपमा सत्य होइन किनभने तपाईंले अझै पनि प्रारम्भिक स्टार्ट-अप पछि नियन्त्रकको पूर्वाग्रह प्रदान गर्न आवश्यक छ, जसको अर्थ सहायक बुटस्ट्र्याप वाइन्डिंगको साथ अनुकूलन इन्डक्टर हो।

- VAUX- DC/DC स्टार्ट-अपको लागि पूर्वाग्रह। सबै माइक्रोचिप PoE PD ICs सँग उपलब्ध विनियमित भोल्युम छtage आउटपुट, VAUX, मुख्य रूपमा बाह्य DC/DC नियन्त्रकको लागि स्टार्ट-अप आपूर्तिको रूपमा प्रयोग गर्न। VAUX एक कम करेन्ट, कम ड्युटी साइकल आउटपुट हो, बाह्य बुटस्ट्र्याप आपूर्तिले कब्जा गर्न नसकेसम्म क्षणभरमा वर्तमान प्रदान गर्दछ।

- PWM नियन्त्रक र DC/DC- उच्च PoE भोल्युम रूपान्तरण गर्दछtage तल विनियमित आपूर्ति voltage अनुप्रयोग द्वारा प्रयोग गरिएको। PWM बाह्य माइक्रोचिप उपकरण हुन सक्छ वा माइक्रोचिप PD प्याकेजमा एकीकृत हुन सक्छ।

निम्न तालिकाहरूले PSE र PD को लागि PoE मापदण्डहरू तुलना गर्दछ। HDBaseT (PoH) मानकले IEEE 802.3at टाइप 2 केबल प्रकारहरू पछ्याउँछ। यद्यपि, यसको उच्च समर्थित वर्तमानको कारण, यसले एकल केबल बन्डलमा केबलहरूको संख्या सीमित गर्दछ।

तालिका १-१। PSE को लागि IEEE 1af, 1at, र HDBaseT मानकहरू

| PSE आवश्यकताहरू | IEEE® 802.3af वा IEEE 802.3 मा टाइप 1 | IEEE 802.3 मा टाइप 2 | 2-जोडा HDBaseT प्रकार 3 | 4-जोडा HDBaseT प्रकार 3 |

| मा ग्यारेन्टी शक्ति PSE आउटपुट |

15.4W | 30W | 47.5W | 95W |

| PSE आउटपुट भोल्युमtage | 44V देखि 57V | 50V देखि 57V | 50V देखि 57V | 50V देखि 57V |

| मा वर्तमान ग्यारेन्टी | 350 mA DC माथि | 600 mA DC माथि | 950 mA DC माथि | 2x 950 mA DC सँग |

| PSE आउटपुट | 400 mA चुचुरोमा | 686 mA चुचुरोमा | 1000 mA चुचुरोमा | 2000 mA शिखरहरू सम्म |

| अधिकतम केबल पाश प्रतिरोध | 200 | 12.50 | 12.50 | 12.50 |

| भौतिक तह वर्गीकरण | ऐच्छिक | अनिवार्य | अनिवार्य | अनिवार्य |

| समर्थित भौतिक तह वर्गीकरण वर्गहरू | कक्षा ० देखि ४ सम्म | कक्षा ४ अनिवार्य | कक्षा ४ अनिवार्य | कक्षा ४ अनिवार्य |

| डाटा लिङ्क वर्गीकरण | ऐच्छिक | ऐच्छिक | ऐच्छिक | ऐच्छिक |

| २-घटना वर्गीकरण | आवश्यक छैन | अनिवार्य | आवश्यक छैन | आवश्यक छैन |

| २-घटना वर्गीकरण | आवश्यक छैन | आवश्यक छैन | अनिवार्य | अनिवार्य |

| 4-जोडा पावर फिडिङ | अनुमति छैन | अनुमति दिइयो | NA | अनुमति दिइयो |

| सञ्चार | 10/100 BaseT | 10/100/1000 BaseT | ३९/३५/३०/ | ३९/३५/३०/ |

| सञ्चार समर्थित |

10/100 BaseT (Midspan) 10/100/1000 BaseT (स्विच) |

10/100/1000 BaseT मिडस्प्यान्स सहित (टाइप १ र टाइप २) |

३९/३५/३०/ 10000 BaseT |

३९/३५/३०/ 10000 BaseT |

तालिका १-२। PD को लागि IEEE 1af, 2at, र HDBaseT मानकहरू

| PD आवश्यकताहरू | IEEE 802.3af वा IEEE 802.3at टाइप १ |

IEEE 802.3 मा टाइप 2 | HDBaseT प्रकार 3 |

| १०० मिटर केबल पछि PD इनपुटमा ग्यारेन्टी पावर | 12.95W | 25.50W | 72.40W |

| PD इनपुट भोल्युमtage | 37V देखि 57V | 42.5V देखि 57V | 38.125V देखि 57V |

| PD इनपुटमा अधिकतम DC वर्तमान | 350 mA | 600 mA | ०,३२ए |

| भौतिक तह वर्गीकरण | अनिवार्य (कक्षा छैन = कक्षा ०) |

अनिवार्य | अनिवार्य |

| समर्थित भौतिक तह वर्गीकरण वर्गहरू | कक्षा ० देखि ४ सम्म | कक्षा ४ अनिवार्य | कक्षा ४ अनिवार्य |

| डाटा लिङ्क वर्गीकरण | ऐच्छिक | ऐच्छिक | ऐच्छिक |

| २-घटना वर्गीकरण | आवश्यक छैन | अनिवार्य | ऐच्छिक |

| 4-जोडा पावर प्राप्त गर्दै | अनुमति दिइयो | अनुमति दिइयो | समर्थन गर्दछ |

| संचार समर्थित | 10/100 BaseT (Midspan) 10/100/1000 BaseT (स्विच) |

10/100/1000 BaseT Midspans सहित (टाइप 1 र टाइप 2 दुवै) | 10/100/1000/10000 BaseT |

डीसी भोल्युमtage मार्फत तार जोडी या त ध्रुवीय हुन सक्छ। PI मा उपलब्ध PoE पावरको सबै सम्भावित संयोजनहरू समायोजन गर्न, PD 70224 Ideal Diode Bridge वा PD साइडमा डुअल डायोड ब्रिजहरूको प्रयोग आवश्यक छ।

पत्ता लगाउने चरणमा, मानकहरूले केबल मानक अनुरूप PD मा जडान गरिएको छ कि छैन भनेर निर्धारण गर्ने विधिहरू परिभाषित गर्दछ, जुन शक्ति प्राप्त गर्न सक्षम उपकरण हो, एक गैर-शक्ति प्राप्त गर्ने क्षमता यन्त्रमा जडान गरिएको छ वा विच्छेदन गरिएको छ।

यी मापदण्डहरूले पावर आवश्यकताहरू निर्धारण गर्ने विधिहरू वा जडान गरिएको PoE-अनुरूप PD ले कति शक्ति प्राप्त गर्न सक्षम छ र PD ले PSE द्वारा समर्थित शक्ति स्तर निर्धारण गर्न सक्ने तरिकाहरू थप परिभाषित गर्दछ। यसलाई वर्गीकरण चरण भनिन्छ।

एक अनुरूप PSE ले PI मा अपरेटिङ पावर लागू गर्दैन जबसम्म यसले PoE अनुरूप PD सफलतापूर्वक पत्ता लगाएको छैन। पत्ता लगाउने चरणमा, PSE ले कम भोल्युमको श्रृंखला लागू गर्दछtage 2.80V र 10.0V बीचको दालहरू परीक्षण गर्नुहोस्। यी दालहरूको प्रतिक्रियामा, एक PoE-अनुरूप PD ले वैध हस्ताक्षर प्रदान गर्नुपर्छ, जसलाई 23.7 k र 26.3 k बीचको भिन्नता प्रतिरोध र 50 nF र 120 nF बीचको इनपुट क्यापेसिटन्स चाहिन्छ। वैध पत्ता लगाउने प्रतिरोध प्रदान गर्न, सबै माइक्रोचिप PoE PD नियन्त्रकहरूलाई बाह्य 24.9 k प्रतिरोधक चाहिन्छ। यो प्रतिरोधक PD उपकरणको VPP र RDET पिनहरू बीच जोडिएको छ। जब एक माइक्रोचिप PD नियन्त्रकले इनपुट भोल्युम अवलोकन गर्दछtage पत्ता लगाउने दायरा 2.7V देखि 10.1V सम्म, यसले आन्तरिक रूपमा यो प्रतिरोधकलाई PI मा जडान गर्दछ। पत्ता लगाउने चरण समाप्त भएपछि, माइक्रोचिप नियन्त्रकले अतिरिक्त पावर हानिबाट बच्न पत्ता लगाउने प्रतिरोधकलाई स्वचालित रूपमा विच्छेद गर्दछ। एक 100V सिरेमिक क्यापेसिटर VPP र VPN बीच PD यन्त्रको पिनमा एक मान्य पत्ता लगाउने क्यापेसिटन्स (सिफारिस गरिएको मान 82 nF देखि 100 nF) प्रदान गर्न जोडिएको हुनुपर्छ।

मान्य हस्ताक्षर पत्ता लागेपछि, PSE ले वर्गीकरण चरण सुरु गर्न सक्छ। वर्गीकरण 802.3af र 802.3at प्रकार 1 PSEs र PDs को लागि वैकल्पिक छ; र 802.3at प्रकार 2 र PoH को लागी अनिवार्य छ। PSE ले भोल्युम बढाउँछtage भोल्युममाtage निर्दिष्ट समय अवधिको लागि 15.5V देखि 20.5V को दायरा। यसलाई वर्गीकरण औंला भनिन्छ। यदि एक भन्दा बढी औंलाहरू आवश्यक भएमा, वर्गीकरण औंलाहरूलाई चिन्ह भोल्युम भनेर चिनिन्छ भनेर छुट्याइन्छ।tage, जहाँ PSE ले भोल्युम घटाउँछtage 6.3V देखि 10.1V बीचको दायरामा, फेरि निर्दिष्ट समयको लागि।

जबकि वर्गीकरण भोल्युमtage वा वर्ग औँला लागू गरिन्छ, PD ले आफ्नो वर्ग सङ्केत गर्न एक स्थिर करेन्ट कोर्नु पर्छ। माइक्रोचिप नियन्त्रकहरूमा वर्गीकरण हस्ताक्षर पिनहरूमा PD उपकरणहरू RCLS र VPN बीच जडान भएको प्रतिरोधक RCLS द्वारा प्रोग्राम गरिएको छ। जब इनपुट भोल्युमtage वर्गीकरण दायरामा छ, PD ले RCLS द्वारा हालको प्रोग्राम गरिएको छ।

एक IEEE 802.3at टाइप 2 अनुरूप PD लाई 2-घटना वर्गीकरण पहिचान गर्न र आन्तरिक सर्किटहरूलाई AT फ्ल्याग सिग्नल प्रदान गर्न आवश्यक छ जसले PD AT प्रकार 2 अनुरूप PSE सँग जडान भएको जनाउँछ।

3-घटना वर्गीकरण पहिचान गर्न र आन्तरिक सर्किटहरूलाई HDBaseT फ्ल्याग सिग्नल प्रदान गर्नको लागि एक PoH प्रकार 3 अनुरूप PD आवश्यक छ जसले PD HDBaseT प्रकार 3 अनुरूप PSE मा जडान भएको संकेत गर्दछ।

यदि पोर्ट भोल्युमtage PI ड्रपमा 2.8V भन्दा कम छ, PSE वर्ग जानकारी रिसेट हुन्छ र PD ले वर्ग निर्भर झण्डा रिसेट गर्नुपर्छ।

माइक्रोचिप PoE PDs मा एक पृथक स्विच हुन्छ जसले पत्ता लगाउने र वर्गीकरण चरणहरूमा, वा पावर हानि र ओभरलोडको समयमा PI बाट PD को फिर्ती पक्ष विच्छेद गर्दछ। PD ले PI vol मा आइसोलेटिंग स्विच अन गर्छtage लेभल ४२V वा माथि छ र PI भोल्युममा आइसोलेटिंग स्विच बन्द गर्नुहोस्tag30.5V तल e स्तर। तिनीहरू सक्रिय रूपमा स्टार्ट-अपको समयमा 350 mA वा कममा वर्तमान सीमित गर्छन्।

निम्न तथ्याङ्कहरूले क्रमशः टाइप 1 IEEE 802.3af र टाइप 2 IEEE 802.3at को लागि आधारभूत PoE पत्ता लगाउने, वर्गीकरण, र पावर-अप अनुक्रमहरू देखाउँछन्। कक्षा स्तरहरू, तिनीहरूको सम्बन्धित धाराहरू, र सिफारिस गरिएका RCLS प्रतिरोधकहरू तालिका 1-3 मा सूचीबद्ध छन्।

चित्र १-४। आधारभूत PoE पत्ता लगाउने, वर्गीकरण, र IEEE 1af मानकका लागि पावर-अप अनुक्रमहरू

चित्र १-५। 1 मा मानक को लागी आधारभूत PoE पत्ता लगाउने, वर्गीकरण, र पावर-अप अनुक्रमहरू

तालिका १-३। वर्गीकरण वर्तमान परिभाषाहरू र आवश्यक वर्ग सेटिङ प्रतिरोधकहरू

| कक्षा | वर्गीकरणको क्रममा PD हालको ड्र | RCLASS प्रतिरोध मानहरू, Ω | ||

| न्यूनतम | नाममात्र | अधिकतम | ||

| 0 | 0 mA | NA | 4 mA | स्थापना गरिएको छैन |

| 1 | 9 mA | 10.5 mA | 12 mA | 133 |

| 2 | 17 mA | 18.5 mA | 20 mA | 69.8 |

| 3 | 26 mA | 28 mA | 30 mA | 45.3 |

| 4 | 36 mA | 40 mA | 44 mA | 30.9 |

नोट: PD इनपुट भोल्युमtage वर्गीकरण चरण को समयमा 14.5V देखि 20.5V छ।

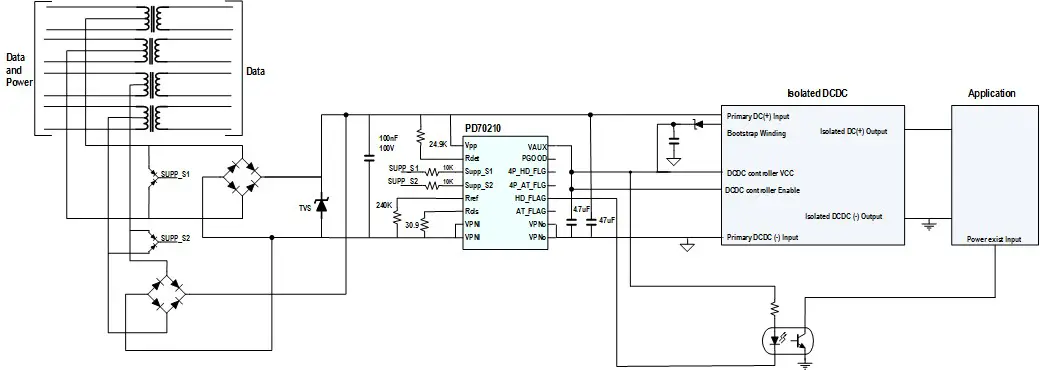

PD702x0 र PD701x0 ICs प्रयोग गर्दै

PD702x0 र PD701x0 ICs 2-जोडा र 4-जोडा प्रणालीहरूको लागि प्रयोग गर्न सकिन्छ, निम्न चित्रमा देखाइएको छ। दुई डायोड ब्रिजबाट आउटपुट VPP (सकारात्मक बस) र VPNIN (नकारात्मक बस) मा जडान गरिएको छ। DC/DC कनवर्टर/एप्लिकेशनमा आउटपुट जडानहरू VPP र VPNOUT बीच बनाइन्छ। चित्र २-१। एकल PD2/A/AL IC सँग सामान्य 1- वा 2-जोडा कन्फिगरेसन

आधारभूत इनपुट/आउटपुट जडानहरूको अतिरिक्त, सामान्य अनुप्रयोगको लागि निम्न बाह्य अवयवहरू आवश्यक हुन्छन्:

- पत्ता लगाउने प्रतिरोधक: VPP र RDET पिन बीच 24.9 k ± 1% प्रतिरोधक जडान गर्नुहोस्। यो प्रतिरोधक पहिचान हस्ताक्षर प्रदान गर्न प्रयोग गरिन्छ। कम वाटtagई प्रकार प्रयोग गर्न सकिन्छ किनकि पत्ता लगाउने चरण सक्रिय हुँदा यस रेसिस्टरमा 7 मेगावाट भन्दा कम तनाव हुन्छ, र पावर अन भएपछि रेसिस्टर विच्छेद हुन्छ।

- सन्दर्भ प्रतिरोधक: आन्तरिक सर्किटरीको लागि प्रतिरोधक सेटिङ बायस करन्ट RREF पिन र VPNIN बीच जडान हुनुपर्छ। PD60.4/A/AL ICs को लागि 1 k ±70210% रेसिस्टर र PD240/PD1 को लागि 70100 k ±70200% जडान गर्नुहोस्। यो प्रतिरोधक IC को नजिक स्थित हुनुपर्छ। कम वाटtagई प्रकार प्रयोग गर्न सकिन्छ (पावर अपव्यय 1 मेगावाट भन्दा कम छ)।

- वर्गीकरण वर्तमान प्रतिरोधक: RCLASS पिन र VPNIN बीच जोडिएको रेसिस्टरको मानले वर्गीकरण चरणको समयमा PD हालको ड्र निर्धारण गर्दछ। IEEE अनुरूप वर्गीकरण स्तरहरूसँग सम्बन्धित मानहरू अघिल्लो तालिकामा प्रदान गरिएका छन्।

- इनपुट क्यापेसिटर: IEEE लाई 50 nF र 120 nF बीचको क्यापेसिटन्स VPP र VPNIN बीच मान्य पहिचान हस्ताक्षरको लागि उपस्थित हुन आवश्यक छ। उत्कृष्ट प्रदर्शनको लागि र तीव्र भोल्युमबाट चिपलाई जोगाउनtagई ट्रान्जिन्टहरू, माइक्रोचिपले सिरेमिक क्यापेसिटर 82 nF देखि 100 nF प्रति 100V प्रयोग गर्न सिफारिस गर्दछ। यो चिपको व्यावहारिक रूपमा नजिक अवस्थित हुनुपर्छ।

- इनपुट TVS: यदि डायोड ब्रिजहरू प्रयोग गरिन्छ, आधारभूत स्तरको विरुद्ध आधारभूत सुरक्षाको लागिtage ट्रान्जिन्टहरू (<1 kV), दुबै 10×700 µS वा 1.2×50 µS, 58V TVS (जस्तै SMBJ58A वा समकक्ष) VPP पिन र VPNIN बीच जोडिएको हुनुपर्छ। यदि सक्रिय पुल PD70224 प्रयोग गरिएको छ वा IEC/EN 61000-4-5 (2014 Ed.3), ITU-T K21, र GR-1089 को वृद्धि आवश्यकताहरू पूरा गर्न प्रयोग गरिएको छ भने, त्यसपछि हेर्नुहोस् माइक्रोचिप आवेदन नोट AN3410.

- SUPP_S1 र SUPP_S2 इनपुटहरू (PD70210/A/AL मात्र): 10 k प्रतिरोधकहरू प्रत्येक इनपुट पिन SUPP_S1 र SUPP_S2 मा श्रृंखलामा जडान हुनुपर्छ। यी पिनहरूका लागि संकेतहरू सक्रिय पुल PD70224 को सम्बन्धित पिनहरूबाट वा सहायक रेक्टिफायरबाट आउँछन् यदि नियमित डायोड ब्रिजहरू अघिल्लो चित्रमा देखाइएको रूपमा प्रयोग गरिन्छ। PD70210/A/AL मा यी इनपुटहरूले AT र 4-जोडा AT झण्डाहरू सेट गर्न अनुमति दिन्छ केही लिगेसी 4-जोडा मिडस्प्यान्सहरू जसले प्रत्येक जोडी सेटमा केवल एक वर्गीकरण पल्स प्रदान गर्दछ। यदि SUPP_S1 र SUPP_S2 पिनहरू खुला छोडिएमा, PD70210/A/AL मा झण्डाहरूको स्थिति निम्न तालिका अनुसार छ।

तालिका २-१। SUPP_S2 र SUPP_S1 पिनहरू जडान नभएको बेला PD70210/A/AL झण्डाहरूको स्थिति

| औंलाहरूको संख्या (N-घटना वर्गीकरण) |

AT झण्डा | HDBaseT झण्डा | 4-जोडा AT झण्डा | 4-जोडा HDBaseT झण्डा |

| 1 | नमस्ते Z | नमस्ते Z | नमस्ते Z | नमस्ते Z |

| 2 | १२ वी | नमस्ते Z | नमस्ते Z | नमस्ते Z |

| 3 | १२ वी | १२ वी | नमस्ते Z | नमस्ते Z |

| 4 | १२ वी | १२ वी | १२ वी | नमस्ते Z |

| 5 | १२ वी | १२ वी | १२ वी | नमस्ते Z |

| 6 | १२ वी | १२ वी | १२ वी | १२ वी |

- पावर गुड (PD70100, PD70200, र PD70210 मात्र): PGOOD पिनमा खुला ड्रेन पावर गुड सिग्नल उपलब्ध छ। स्टार्ट-अप पछि, PGOOD फ्ल्यागले कम भोल्युम उत्पन्न गर्दछtage VPNOUT को सन्दर्भमा एप्लिकेसनलाई सूचित गर्न कि पावर रेलहरू तयार छन्। पुल-अप भोल्युमtage यस पिनमा PD20 को लागि 70210V र VPP भोल्युममा सीमित छtage PD7010x/PD7020x को लागि। पावर गुडलाई DC-DC को बुटस्ट्र्याप वाइन्डिङ आउटपुटद्वारा पनि तान्न सकिन्छ, यस अवस्थामा, यसलाई VAUX बाट Schottky diode मार्फत स्टार्टअपको बेला VAUX बाट थप वर्तमान ड्रलाई रोक्नको लागि अलग गर्नुपर्छ।

नोट: यदि PGOOD बाह्य अनुप्रयोग सुरु गर्न प्रयोग गरिन्छ भने, अनुप्रयोगले IEEE 80 द्वारा आवश्यक अपरेटिङ स्टेट ढिलाइमा 802.3 ms inrush प्रदान गर्नुपर्छ। - झण्डा रिपोर्टिङ PSE प्रकार: यी झण्डा s हुन सक्छampउपभोग गर्न अधिकतम शक्ति मा निर्णय गर्न आवेदन द्वारा नेतृत्व। यी सबै झण्डाहरू ओपन ड्रेन पिनहरू हुन्। पुल-अप भोल्युमtage यी सबै पिनहरूमा PD20/A/AL को लागि 70210V मा सीमित छ, र VPP भोल्युममाtage PD70200/PD70100 को लागि। झण्डाहरू DC-DC को बुटस्ट्र्याप घुमाउरो आउटपुटद्वारा तान्न सकिन्छ, जसमा, यो VAUX बाट Schottky डायोड मार्फत अलग हुनुपर्छ। फ्ल्याग स्टेट पोर्ट स्टार्टअपमा एक पटक मात्र सेट गरिएको छ र अपरेटिङ स्टेट ढिलाइ समाप्त भएको एप्लिकेसनलाई संकेत गर्न कम्तिमा 80 ms ढिलाइको साथ दाबी गरिन्छ। यदि SUPP_S1 र SUPP_S2 पिनहरू पोर्ट अन गरेपछि परिवर्तन हुँदैछन् भने, झण्डाहरू तदनुसार परिवर्तन हुँदैनन्।

- AT_FLAG (PD70210/A/AL र PD70200 मा उपलब्ध छ): टाइप 2 PSE र PD ले एक अर्कालाई वर्गीकरण मार्फत पारस्परिक रूपमा पहिचान गर्दा यो झण्डा सक्रिय हुन्छ।

- HD_FLAG (PD70210/A/AL मा उपलब्ध छ): HDBaseT PSE र PD ले एकअर्कालाई वर्गीकरण मार्फत पारस्परिक रूपमा पहिचान गर्दा यो झण्डा सक्रिय हुन्छ।

- 4P_AT_FLAG (PD70210/A/AL मा उपलब्ध छ): PSE र PD को 4-जोडा संस्करणले वर्गीकरण मार्फत एकअर्कालाई पारस्परिक रूपमा पहिचान गर्दा यो झण्डा सक्रिय कम हुन्छ।

- 4P_HD_FLAG (PD70210/A/AL मा उपलब्ध): यो झण्डा सक्रिय कम हुन्छ जब 4-जोडा (ट्विन) HDBaseT PSE

र PD एक अर्कालाई वर्गीकरण मार्फत पहिचान गर्दछ।

- VAUX आउटपुट: VAUX बाहिरी DC-DC कन्भर्टर कन्ट्रोलरको लागि स्टार्ट-अप आपूर्तिको रूपमा प्रयोगको लागि उपलब्ध कम पावर विनियमित आउटपुट हो। स्टार्ट-अप पछि, VAUX लाई DC-DC कन्भर्टरको सहायक (बुटस्ट्र्याप) वाइन्डिङबाट समर्थन गरिनुपर्छ। VAUX आउटपुटको लागि न्यूनतम 4.7 µF को सिरेमिक क्यापेसिटर VAUX पिन र VPNOUT पिन बीच सीधा जडान गर्न र भौतिक रूपमा उपकरणको नजिक राख्न आवश्यक छ।

बाह्य DC स्रोतको साथ सञ्चालन

PD70210A/AL IC को उपयोग गर्ने PD अनुप्रयोगहरूले बाह्य सहायक शक्ति स्रोत (DC वाल एडाप्टर) प्राथमिकता प्रकार्य प्रदान गर्दछ। सामान्यतया, बाह्य स्रोतसँग शक्ति प्रदान गर्ने तीन तरिकाहरू छन्:

- बाह्य स्रोत सीधा PD इनपुट (VPP देखि VPNIN) मा जोडिएको छ। यसका लागि बाह्य स्रोत आउटपुट भोल्युम चाहिन्छtage कुनै लोडमा न्यूनतम 42V र अधिकतम लोडमा 36V भन्दा बढी हुनुपर्दछ। एडाप्टरलाई OR-ing डायोड मार्फत VPP वा VPNIN बाट अलग गरिएको हुनुपर्छ। यो कन्फिगरेसनले एडाप्टर प्राथमिकता प्रदान गर्दैन र PD70210, PD70100, र PD70200 सँग प्रयोग गर्न सकिन्छ।

- बाह्य स्रोत सीधा PD आउटपुट (VPP र VPNOUT बीच) मा जोडिएको छ। बाह्य स्रोतलाई OR-ing डायोड मार्फत VPP वा VPNOUT बाट अलग गरिनु पर्छ। एडाप्टर प्राथमिकताको लागि, PD70210A/AL मात्र प्रयोग गर्नुपर्छ।

- बाह्य स्रोत सिधै एप्लिकेसनको कम भोल्युमसँग जोडिएको छtage आपूर्ति रेलहरू (DC-DC कनवर्टरको आउटपुट)। बाह्य स्रोतलाई एप्लिकेसन पावर सप्लाईको आउटपुटबाट या त स्विच गरिएको जडान, डायोड वा छुट्टै नियामक मार्फत पृथक गरिनु पर्छ जसले वर्तमान मात्र स्रोत दिन्छ (करेन्ट सिंक गर्दैन)।

निम्न तीन तथ्याङ्कले पूर्व देखाउँछampPD70210A/AL को लेस बाह्य भित्ता एडाप्टरसँग कन्फिगर गरिएको छ। थप विवरणहरू र भोल्युमको सिफारिस गरिएको मानहरूको लागिtage dividers, AN3472 हेर्नुहोस्: PoE मा सहायक शक्ति कार्यान्वयन। चित्र ३-१। सहायक पावर PD3 इनपुटमा जडान भयो

चित्र ३-१। सहायक पावर PD3 इनपुटमा जडान भयो

चित्र ३-२। सहायक पावर PD3A आउटपुटमा जडान भयो

चित्र ३-३। सहायक पावर एप्लिकेसन आपूर्तिसँग जोडिएको छ

सामान्य सञ्चालन सिद्धान्त

घटना थ्रेसहोल्डहरू

PD ICs भोल्युमको आधारमा विभिन्न राज्यहरू बीच स्विच हुन्छtage VPP र VPNIN पिनहरू बीच।

- VPPVPNIN = 1.3V देखि 10.1V (बढ्दो भोल्युमtage): पत्ता लगाउने प्रतिरोधक RDET VPP र VPNIN बीच जोडिएको छ।

- VPPVPNIN = 10.1V देखि 12.8V (बढ्दो भोल्युमtage): पत्ता लगाउने प्रतिरोधक RDET VPNIN बाट विच्छेद भएको छ।

- VPPVPNIN = 11.4V देखि 13.7V (बढ्दो भोल्युमtage): वर्गीकरण हालको स्रोत VPP र VPNIN बीच जोडिएको छ। यो थ्रेसहोल्डले RCLASS द्वारा सेट गरिएको प्रोग्राम गरिएको वर्तमान ड्रलाई स्थापना गर्दछ। हालको परिमाणले प्रति IEEE 802.3at र HDBaseT मापदण्डहरूमा वर्ग स्तर सेट गर्दछ। यो प्रकार्य IEEE 802.3af अनुरूप PDs को लागि वैकल्पिक छ र IEEE 802.3at र HDBaseT अनुरूप PDs को लागी अनिवार्य छ। वर्गीकरण हालको स्रोत VPP बढ्दो भोल्युमको समयमा जडान रहन्छtage 20.9V सम्म।

- VPPVPNIN = 20.9V देखि 23.9V (बढ्दो भोल्युमtage): वर्गीकरण हालको स्रोत विच्छेद भएको छ। वर्गीकरण हालको स्रोतको थ्रेसहोल्डहरू सक्षम र असक्षम गर्ने बीच केही हिस्टेरेसिस छ।

- VPPVPNIN = 4.9V देखि 10.1V (falling voltage): यो मार्क भोल्युम होtage दायरा। IC ले VPPVPNIN भोल्युम पहिचान गर्नेछtage वर्गीकरण वर्तमान स्रोत जडान थ्रेशोल्डबाट झर्दै 2 घटना वर्गीकरण हस्ताक्षरको एउटा घटनाको रूपमा थ्रेसहोल्ड चिन्ह लगाउन। स्तरका घटनाहरू चिन्ह लगाउनको लागि कक्षाको सङ्ख्याले IC लाई तिनीहरूको सक्रिय निम्न स्थितिमा सान्दर्भिक झण्डाहरू सेट गर्नको लागि निम्त्याउँछ।

- VPPVPNIN = 36V देखि 42V (बढ्दो भोल्युमtage): Isolation स्विच अफ स्टेटबाट Inrush Current Limit (सफ्ट स्टार्ट) मोडमा स्विच गरिएको छ। यस मोडमा, अलगाव स्विचले DC वर्तमानलाई 240 mA (सामान्य) मा सीमित गर्दछ। सफ्ट स्टार्ट मोडको समयमा हालको सीमा सर्किटरीले भोल्युमलाई निगरानी गर्दछtage अलगाव स्विच (VPNOUTVPNIN) मा भिन्नता र इनरश करन्ट कायम राख्छ। inrush वर्तमान सीमा आन्तरिक MOSFET रैखिक मोड मा सञ्चालन गर्दछ।

जब VPNOUTVPNIN ०.७V वा तल झर्छ, आइसोलेशन स्विच इनरश वर्तमान सीमा असक्षम पारिएको छ, VAUX सक्षम पारिएको छ, हालको सुरक्षामा 0.7A (अधिकतम) को साथ आइसोलेसन स्विच पूर्ण रूपमा सक्रिय हुन्छ र फ्लोग ढिलाइ पछि सान्दर्भिक झण्डाहरू दाबी गरिन्छ, जुन न्यूनतम 2.2 हो। सुश्री। - VPPVPNIN = 30.5V देखि 34.5V (falling voltage): अलगाव स्विच बन्द छ, VPNIN र VPNOUT बीच उच्च प्रतिबाधा स्थापना। बल्क क्यापेसिटर डिस्चार्ज प्रकार्य सक्षम छ र भोल्युम बीचको भिन्नता सम्म सक्षम रहन्छtages VPP र VPNOUT 30V र 7V बीच रहन्छ। यदि सहायक शक्ति स्रोत प्रयोग गरिन्छ, यसको भोल्युमtage कि त 34.5V माथि हुनुपर्छ, वा डिस्चार्ज वर्तमान प्रवाह रोक्न VPNOUT र सहायक पावर स्रोतको फिर्ताको बीचमा आइसोलेशन डायोड थप्नु पर्छ।

- VPPVPNIN = 2.8V देखि 4.85V (falling voltage): पत्ता लगाउने प्रतिरोधक RDET यस थ्रेसहोल्डमा पुन: जडान गरिएको छ। VPPVPNIN voltage 1.1V तल खस्छ।

Inrush वर्तमान सीमा

प्रणाली स्टार्ट-अपमा बल्क क्यापेसिटरहरूको प्रारम्भिक चार्ज-अपको समयमा वर्तमान सीमित गर्नको लागि इनरश वर्तमान सीमा आवश्यक छ र PoE मापदण्डहरू द्वारा आवश्यक छ। ठूला इनरश धाराहरूले ठूलो भोल्युम सिर्जना गर्न सक्छtage PI मा sags, जसले बदलामा घटना थ्रेसहोल्ड (जस्तै AT_FLAG) मा बाँधिएको प्रणाली कार्यहरूलाई तिनीहरूको प्रारम्भिक अवस्थाहरूमा रिसेट गर्नको लागि निम्त्याउन सक्छ। सफ्ट स्टार्ट हालको सीमाले भोल्युमलाई उल्लेखनीय रूपमा घटाउनेछtage स्टार्ट-अपमा ढिलो।

पूर्ण रूपमा डिस्चार्ज गरिएको बल्क क्यापेसिटरमा स्टार्ट-अपले बल्क क्यापेसिटन्सको साइजमा निर्भर समयको लागि आइसोलेशन स्विचमा ठूलो पावर डिसिपेसनमा परिणाम दिन्छ। अधिकतम प्रारम्भिक मात्राtagई ड्रप भर आइसोलेशन स्विच लगभग 42V हुन सक्छ। पृथक स्विच द्वारा फैलिएको अधिकतम पावर बल्क क्यापेसिटर चार्जको रूपमा घट्छ, अन्ततः स्विच पूर्ण रूपमा सक्रिय हुँदा सामान्य अपरेटिङ पावर डिसिपेसनमा घट्छ। सफ्ट स्टार्ट मोडबाट सामान्य सञ्चालन मोडमा स्विच गर्न आवश्यक समयको अवधि निम्न सूत्र प्रयोग गरेर गणना गर्न सकिन्छ:

T = ((V 0.7) × C) / I

कहाँ:

I = सफ्ट स्टार्टको समयमा IC को वर्तमान (सामान्यतया 240 mA)

C = कुल इनपुट बल्क क्यापेसिटन्स

V = प्रारम्भिक VPNOUTVPNIN भोल्युमtage सफ्ट स्टार्टको सुरुमा (VMAX = VPP)

बल्क क्यापेसिटरको अधिकतम मान 240 μF हो।

बल्क क्यापेसिटर डिस्चार्ज

PD70210/A/AL ICs ले एप्लिकेसन बल्क क्यापेसिटरको डिस्चार्ज प्रदान गर्दछ जब VPPVPNIN घट्ने भोल्युमtage अलगाव स्विच टर्न-अफ तल झर्छ। यो सुविधाले सुनिश्चित गर्दछ कि एप्लिकेसन बल्क क्यापेसिटन्स पत्ता लगाउने प्रतिरोधक मार्फत डिस्चार्ज हुँदैन, जसले पत्ता लगाउने हस्ताक्षर असफल हुन सक्छ र PSE लाई PD सुरु गर्नबाट रोक्न सक्छ। सक्षम हुँदा, डिस्चार्ज प्रकार्यले 22.8 mA को न्यूनतम नियन्त्रित डिस्चार्ज वर्तमान प्रदान गर्दछ, जुन VPP पिन मार्फत, आन्तरिक रूपमा अलगाव MOSFET को शरीर डायोड मार्फत, र VPNOUT पिन मार्फत बाहिर निस्कन्छ। डिस्चार्ज सर्किटरी मोनिटर भोल्युमtage VPPVPNOUT बीचको भिन्नता, र सक्रिय रहन्छ जबकि भिन्नता voltage 7V (VPPVPNOUT) 30V हो। डिस्चार्ज गर्न अधिकतम समय गणना गर्न निम्न समीकरण प्रयोग गर्नुहोस्:

T = ((V 7V) × C)/0.0228

कहाँ:

C = कुल इनपुट बल्क क्यापेसिटन्स

V = प्रारम्भिक VPPVPNOUT भोल्युमtage अलगाव स्विच बन्द-अफ मा

Example: प्रारम्भिक क्यापेसिटर भोल्युमको लागिtag32V को e, यसले 240 µF क्यापेसिटरलाई 220V स्तरमा डिस्चार्ज गर्न 7 ms लिन्छ।

डिस्चार्ज अपरेशनमा टाइमर छ र यो कम्तिमा 430 ms को लागि सक्रिय छ।

सहायक भोल्युमtage-VAUX

सबै माइक्रोचिप PD IC सँग उपलब्ध विनियमित भोल्युम छtage आउटपुट, VAUX, मुख्य रूपमा बाह्य DC/DC नियन्त्रकको लागि स्टार्ट-अप आपूर्तिको रूपमा प्रयोग गर्न। VAUX एक कम करेन्ट, कम ड्युटी साइकल आउटपुट हो, बाह्य बुटस्ट्र्याप आपूर्तिले कब्जा गर्न नसकेसम्म क्षणभरमा वर्तमान प्रदान गर्दछ। स्थिर सञ्चालनको लागि VAUX र पावर ग्राउन्ड पिनहरू बीच 4.7 F वा ठूलो क्यापेसिटर जडान गर्नुहोस्।

VAUX आउटपुट नाममात्र 10.5V मा विनियमित छ, र 10 ms को लागि 10 mA को शिखर वर्तमान आपूर्ति गर्दछ। (5 एमएस। PD70200/ PD70100 को लागि)। निरन्तर प्रवाह PD4x को लागि 7021 mA र PD2x/PD7020x को लागि 7010 mA हो। सामान्यतया, VAUX आउटपुट उच्च भोल्युमको बुटस्ट्र्याप आपूर्तिसँग जोडिएको हुन्छtage (जस्तै पृथक DC/DC कनवर्टर ट्रान्सफर्मरबाट सुधारिएको सहायक आउटपुट)। VAUX आउटपुट वर्तमान सिंक गर्दैन। एक पटक बुटस्ट्र्याप भोल्युमtage VAUX आउटपुट भोल्युम भन्दा बढि छtage स्तर, VAUX आउटपुटले अब वर्तमान प्रदान गर्दैन र DC-DC कनवर्टरको सञ्चालनमा पारदर्शी हुनेछ। न्यूनतम आउटपुट भोल्युमको लागि सबै अपरेटिङ अवस्थाहरूमा सुधारिएको बुटस्ट्र्याप आउटपुट डिजाइन गर्न सिफारिस गरिन्छ।tag12.5V को e।

सफ्ट स्टार्ट मोडमा वा आइसोलेशन स्विच बन्द हुँदा, VAUX आउटपुट VPP खस्दै असक्षम हुन्छ।

PGOOD आउटपुट

PD70210, PD70100, र PD70200 ICs ले पावर राम्रो स्थिति जनाउने ओपन ड्रेन आउटपुट प्रदान गर्दछ। यो आउटपुटले सक्रिय कम दाबी गर्दछ जब भोल्युमtage VPP र VPNOUT बीच लगभग 40V पुग्छ। दाबी गरेपछि, PGOOD आउटपुट 5 mA को हालको सिंक क्षमताको साथ ग्राउन्डमा स्विच हुन्छ। जब VPPVPNIN voltage पृथक स्विच टर्न-अफ थ्रेसहोल्ड भन्दा तल आउँछ, PGOOD आउटपुट उच्च प्रतिबाधा स्थितिमा सेट हुन्छ।

यो आउटपुट पत्ता लगाउन प्रयोग गर्न सकिन्छ जब PI voltage सञ्चालन दायरामा छ।

PD70210A/AL ले PGOOD आउटपुट समावेश गर्दैन। यदि यस्तो कार्यक्षमता आवश्यक छ भने, VAUX आउटपुट विकल्पको रूपमा प्रयोग गर्न सकिन्छ। यदि तपाईंले VAUX लाई बाह्य सानो सङ्केत N- च्यानल FET को गेटमा र यसको स्रोत VPNOUT मा बाँध्नुभयो भने, यस FET को नाली PGOOD प्रतिस्थापनको रूपमा प्रयोग गर्न सकिन्छ।

WA_EN इनपुट (PD70210A/AL मात्र)

यो इनपुट पिन VPP र VPNOUT बीचको बाह्य पावर इनपुट जडानको लागि प्रयोग गरिन्छ। चित्र ३-१ हेर्नुहोस्। एक प्रतिरोधक विभाजक R3 र R1 VPP र VPNOUT बीच जोडिएको छ। यी प्रतिरोधकहरूले P- च्यानल FET टर्न-अन थ्रेसहोल्ड सेट गर्दछ। 1V कम सिग्नल P-ch FET गेट र स्रोत R2 मा जडान हुनुपर्छ। P-ch ड्रेन R100 रेसिस्टर मार्फत WA_EN इनपुटमा जोडिएको छ। R1 प्रतिरोधक WA_EN र VPNIN बीच जोडिएको छ। R3 र R4 ले स्तर सेट गर्दछ जसमा मान्य WA इनपुट पत्ता लगाइएको छ। WA_EN इनपुटलाई मानक तर्क स्तर चाहिन्छ। जब WA_EN इनपुट उच्च हुन्छ, PD3A/AL पृथक स्विच बन्द हुन्छ र सबै झण्डाहरू दाबी गरिन्छ–तल्लो तहमा परिवर्तन हुन्छ। प्रतिरोधक चयन गाइड एप्लिकेसन नोट AN4 मा निर्दिष्ट गरिएको छ: PDs को लागि सहायक शक्ति।

SUPP_S1 र SUPP_S2 इनपुटहरू (PD70210A/AL मात्र)

SUPP_S1 र SUPP_S2 इनपुटहरूले PD लाई पावरको स्रोत पहिचान गर्न सक्षम बनाउँछ चाहे यो डेटा हो, स्पेयर जोडीहरू, वा दुवै। यी प्रत्येक इनपुटहरूलाई सान्दर्भिक जोडीमा जडान हुनको लागि साझा क्याथोड डुअल डायोड चाहिन्छ, यदि PD उपकरणहरूampयो इनपुटमा 35V र माथिको उच्च स्तरले यो जोडीलाई सक्रिय जोडीको रूपमा गणना गर्छ। यी इनपुटहरू विशेष PSE सँग काम गर्दा प्रयोग गरिन्छ जसमा दुई जोडीमा मात्र पत्ता लगाउने र वर्गीकरण हुन्छ तर सबै चार जोडीहरूमा शक्ति हुन्छ। SUPP_S1 र SUPP_S2 इनपुटहरू प्रत्येकमा क्रमबद्ध रूपमा जडान गरिएको 10 k रेसिस्टर हुनुपर्छ। जब यी प्रकार्यहरू प्रयोग गरिँदैनन्, SUPP_S1 र SUPP_S2 पिनहरूलाई बाह्य सर्किटहरूबाट विच्छेदन गर्न सकिन्छ र VPNIN इनपुट वा बायाँ फ्लोटिंगमा जडान गर्न सकिन्छ।

PSE प्रकार फ्ल्याग आउटपुटहरू

PD702x0 र PD701x0 ICs ले यसको पत्ता लगाइएको वर्गीकरण ढाँचाद्वारा PSE प्रकारलाई संकेत गर्ने खुला ड्रेन आउटपुटहरू प्रदान गर्दछ। आउटपुट उच्च प्रतिबाधा अवस्थामा छ जबसम्म आइसोलेशन स्विच सफ्ट स्टार्ट वर्तमान सीमा मोडबाट सामान्य सञ्चालन मोडमा सर्दैन। यसलाई पहिचान गरिएको वर्गीकरण ढाँचामा निर्भर गर्दै, कम दाबी गरिनेछ। दाबी गर्दा, झण्डा आउटपुट 5 mA को वर्तमान सिंक क्षमताको साथ ग्राउन्डमा स्विच हुन्छ। VPPVPNIN voltage आइसोलेसन स्विच टर्न-अफ थ्रेसहोल्ड तल आउँछ। झण्डाहरूले PD डिजाइनरलाई अनुप्रयोगसँग सान्दर्भिक झण्डासँग काम गर्न सक्षम बनाउँछ। पत्ता लगाइएको प्रत्येक पावरको लागि, सबै तल्लो पावर फ्ल्यागहरू पनि दाबी गरिएका छन् (IE AT_FLAG AT स्तर र AT माथिको सबै पावर स्तरहरूको लागि दाबी गरिएको छ)। उपलब्ध शक्ति स्तर तालिका 2 मा निर्दिष्ट गरिएको छ। तालिकामा निर्दिष्ट गरिए अनुसार, PD ले वर्गीकरण औंला घटना गणना गर्दछ र यसको गणनाद्वारा PSE प्रकार पहिचान गर्दछ। SUPP_S1 र SUPP_S2 ले PD लाई एक विशेष AT स्तर PSE पहिचान गर्न सक्षम बनाउँछ जसमा दुई जोडीमा मात्र वर्गीकरण छ तर सबै चार जोडीहरूमा शक्ति छ। तसर्थ, यदि दुई औंलाहरू चिनिन्छन् भने, PD उपकरण samples SUPP_S1 र SUPP_S2 इनपुटहरू र यदि दुवै उच्च छन् भने, चार जोडीहरूलाई पावर आपूर्ति गरिन्छ र 4P_AT झण्डा जोडिएको छ।

तालिका ५-१। उपलब्ध PD पावर स्तर र झण्डा संकेत

| वर्ग औंलाहरूको संख्या | SUPP_S1 | SUPP_S2 | PGOOD_ झण्डा |

AT_ झण्डा |

HD_ झण्डा |

4P_AT_ झण्डा |

4P_HD_ झण्डा |

उपलब्ध पावर स्तर |

| 1 | X | X | १२ वी | नमस्ते Z | नमस्ते Z | नमस्ते Z | नमस्ते Z | 802.3 AF स्तर/ 802.3 AT प्रकार 1 स्तर |

| 2 | H | L | १२ वी | १२ वी | नमस्ते Z | नमस्ते Z | नमस्ते Z | 802.3 AT प्रकार 2 स्तर |

| 2 | L | H | १२ वी | १२ वी | नमस्ते Z | नमस्ते Z | नमस्ते Z | 802.3 AT प्रकार 2 स्तर |

| 2 | H | H | १२ वी | १२ वी | नमस्ते Z | १२ वी | नमस्ते Z | डुअल 802.3 AT टाइप 2 स्तर |

| 3 | L | H | १२ वी | १२ वी | १२ वी | नमस्ते Z | नमस्ते Z | HDBaseT प्रकार 3 स्तर |

| 3 | H | L | १२ वी | १२ वी | १२ वी | नमस्ते Z | नमस्ते Z | HDBaseT प्रकार 3 स्तर |

| 3 | H | H | १२ वी | १२ वी | १२ वी | १२ वी | नमस्ते Z | HDBaseT प्रकार 3 स्तर |

| 4 | X | X | १२ वी | १२ वी | १२ वी | १२ वी | नमस्ते Z | डुअल 802.3 AT टाइप 2 स्तर |

| 5 | X | X | भविष्यको लागि आरक्षित | NA | ||||

| 6 | X | X | १२ वी | १२ वी | १२ वी | १२ वी | १२ वी | Twin HDBaseT प्रकार 3 स्तर |

थर्मल संरक्षण

PD702x0 र PD701x0 ICs थर्मल सुरक्षा प्रदान गर्दछ। एकीकृत थर्मल सेन्सर अलगाव स्विच र वर्गीकरण वर्तमान स्रोत को आन्तरिक तापमान निगरानी। यदि कुनै सेन्सरको अति-तापमान थ्रेसहोल्ड नाघेको छ भने, त्यो सेन्सरको सम्बन्धित सर्किट असक्षम हुनेछ।

समस्यामुक्त सञ्चालन सुनिश्चित गर्न, यो सुनिश्चित गर्न महत्त्वपूर्ण छ कि PD IC को खुला प्याड PCB मा तामा क्षेत्रमा माउन्ट गरिएको छ जसले पर्याप्त तातो सिंक प्रदान गर्दछ।

PCB लेआउट दिशानिर्देशहरू

IEEE 802.3at र HDBaseT मापदण्डहरूले निश्चित अलगाव आवश्यकताहरू निर्दिष्ट गर्दछ जुन सबै PoE उपकरणहरूले पूरा गर्नुपर्छ। आगमन डेटा र पावर लाइनहरू, र अनुप्रयोग बाहिरको अन्त प्रयोगकर्ताद्वारा सम्पर्कमा आउन सक्ने कुनै पनि सङ्केत, पावर, वा चेसिस जडानहरू बीचको 1500 VRMS न्यूनतममा आइसोलेशन निर्दिष्ट गरिएको छ। एक सामान्य FR4 PCB मा, यो आवश्यकता सामान्यतया 0.080 VRMS अलगाव आवश्यक पर्ने आसन्न ट्रेसहरू बीच न्यूनतम 2 इन्च (1500 मिमी) को अलगाव अवरोध सिर्जना गरेर सन्तुष्ट हुन्छ।

खुला प्याड (VPNOUT) को पर्याप्त तातो सिंक प्रदान गर्न PCB डिजाइनलाई विशेष ध्यान दिनुहोस्। सबै माइक्रोचिप PD IC प्याकेजहरूले प्याकेजको थर्मल कूलिङ प्रदान गर्न एक्सपोज्ड प्याडको प्रयोग गर्छन्, र यसरी खुला प्याडमा जोडिएको पर्याप्त तामा क्षेत्र समावेश गर्न PCB डिजाइन आवश्यक हुन्छ। मल्टिलेयर बोर्डहरूको लागि, छेउछाउको विमान तहमा प्रवाहकीय वियास प्रयोग गर्न सकिन्छ। ध्यान राख्नुहोस् कि खुला प्याड विद्युतीय रूपमा VPNIN मा जडान गरिएको छ र VPNOUT बाट विद्युतीय रूपमा अलग हुनुपर्छ।

विमान तह र खुला प्याड बीच थर्मल चालकता प्रदान गर्न vias प्रयोग गर्दा, ब्यारेल व्यास मा 12 मिल र (जहाँ सम्भव छ) ग्रिड ढाँचामा राखिएको हुनुपर्छ। ब्यारेल प्वालहरू उचित सोल्डर पेस्ट रिलीजको लागि प्लग वा टेन्ट गरिएको हुनुपर्छ। जब टेन्टेड प्वालहरू प्रयोग गरिन्छ, सोल्डर मास्क समावेश क्षेत्र ब्यारेल मार्फत भन्दा 4 मिल्स (0.1 मिमी) ठूलो हुनुपर्छ।

एकल वा दोहोरो तह बोर्डहरूको लागि, खुला प्याडसँग सीधा सम्पर्कमा ठूलो तामा भरण प्रयोग गर्नुहोस्। २ औंसको तामाको मोटाईले थर्मल कार्यसम्पादनमा सुधार गर्छ। यदि 2 औंस भन्दा कम तामा ट्रेसहरू प्रयोग गर्दै हुनुहुन्छ भने, उपयुक्त ठाउँहरू ट्रेस गर्न थप सोल्डर थपेर समग्र ट्रेस मोटाई बढाउन सिफारिस गरिन्छ।

PCB डिजाइनले उच्च वर्तमान पावर लाइनहरूको लागि चौडा, भारी तामा ट्रेसहरू प्रदान गर्नुपर्छ। एक 4-जोडा, विस्तारित-शक्ति PD मा VPP र VPN टर्मिनलहरूको लागि 2A को अधिकतम ट्रेस प्रवाह हुन सक्छ। VPP, VPNIN, र VPNOUT का लागि वर्तमान बोक्ने ट्रेसहरू अधिकतम वर्तमानमा न्यूनतम तापक्रम वृद्धि व्यावहारिक प्रदान गर्न आकारको हुनुपर्छ। पूर्वका लागिample, न्यूनतम 15 mils चौडा 2 oz तामा अधिकतम 1.6 ° C तापमान वृद्धि संग 10A वर्तमान सम्म समायोजन गर्दछ। यदि 2 औंस भन्दा कमको तामा ट्रेसहरू प्रयोग गरिन्छ भने, न्यूनतम चौडाइ बढाउनुहोस् न्यूनतम तापक्रम वृद्धिको साथ अधिकतम वर्तमान समायोजन गर्न।

PoE संकेतहरूमा voltages 57 गाविस सम्म। कम्पोनेन्ट कार्य भोल्युमtage विचार गर्नुपर्छ, र तदनुसार घटक आकार। सतह माउन्ट प्रतिरोधकहरू राम्रो पूर्व हुन्ample: 0402 प्रतिरोधकहरूसँग सामान्य अधिकतम काम गर्ने भोल्युम छtage 50V को विशिष्टताहरू, जबकि 0805 प्रतिरोधकहरू सामान्यतया 150V मा निर्दिष्ट हुन्छन्।

PD702x0 र PD701x0 ICs सँग प्रयोग गर्दा, पत्ता लगाउने प्रतिरोधक RDET PoE भोल्युममा मात्र जडान हुन्छ।tages 12.8V सम्म, र अन्यथा विच्छेद गरिएको छ, त्यसैले यो कम भोल्युम हुन सक्छtage प्रकार (0402)।

नोट: विस्तृत लेआउट दिशानिर्देशहरूको लागि, माइक्रोचिप एप्लिकेसन नोट AN3533 हेर्नुहोस्।

EMI विचारहरू

संचालित र विकिरणित उत्सर्जनलाई कम गर्न, र सम्भावित ग्राउन्ड लूपहरू "ब्रेक" गर्न, EMI फिल्टर राख्न (वा प्रावधानहरू छोड्न) सिफारिस गरिन्छ। यो फिल्टर सामान्यतया इनपुट रेक्टिफायर ब्रिज र PoE PD कन्ट्रोलरको बिचमा राखिन्छ र निम्न चित्रमा देखाइए अनुसार सामान्य मोड चोक र २ kV सामान्य-मोड क्यापेसिटरहरू समावेश गर्दछ। एक पूर्वampयस्तो फिल्टरको व्यावहारिक कार्यान्वयनको लागि PD7211EVB72FW-12 मूल्याङ्कन बोर्ड प्रयोगकर्ता गाइडमा प्रदान गरिएको छ। त्यसमा पूर्वample, निम्न घटकहरू फिल्टरमा प्रयोग गरिन्छ:

- सामान्य मोड चोक पल्स प्यान P0351

- साधारण मोड capacitors Novice प्यान 1812B682J202NXT

चित्र ८-१। एक विशिष्ट PD8-आधारित प्रणालीमा पावर प्रवाह

सन्दर्भ कागजातहरू

सबै माइक्रोचिप कागजातहरू अनलाइन मा उपलब्ध छन् www.microchip.com/poe.

- IEEE 802.3at-2015 मानक, खण्ड 33 (MDI मार्फत DTE पावर)

- HDBaseT विशिष्टता

- PD70210/PD70210A/PD70210AL डाटा पाना

- PD70211 डाटाशीट

- PD70100/PD70200 डाटा पाना

- PD70101/PD70201 डाटा पाना

- PD70224 डाटाशीट

- PD प्रणाली सर्ज इम्युनिटी PD3410xx_PD701xx को लागि AN702 डिजाइन

- AN3472 PoE मा सहायक शक्ति कार्यान्वयन गर्दै

- AN3471 PD1x2 र PD802.3x3 ICs प्रयोग गरी टाइप 702/1 701 वा HDBaseT टाइप 1 PD फ्रन्ट एन्ड डिजाइन गर्दै

- AN3533 PD70210(A), PD70211 प्रणाली लेआउट दिशानिर्देशहरू

संशोधन इतिहास

| संशोधन | मिति | विवरण |

| B | १/४ | यस संशोधनमा गरिएका परिवर्तनहरूको सारांश निम्न छ: • अपडेट गरिएको तालिका १। • अद्यावधिक गरिएको 7. PCB लेआउट दिशानिर्देशहरू: 0603 प्रतिरोधकहरूको उल्लेख हटाइयो। नोट थपियो। • थपियो 8. EMI विचारहरू। • अद्यावधिक गरिएको 9. सन्दर्भ कागजातहरू। |

| A | १/४ | यो यस कागजातको प्रारम्भिक मुद्दा हो। PD1x2 र PD802.3x3 ICs प्रयोग गरी Type702/0 701 वा HDBaseT Type 0 Powered Device Front End डिजाइन गर्नु पहिले निम्न कागजातहरूमा वर्णन गरिएको थियो: • AN209: PD1/ PD2A ICs प्रयोग गरी टाइप 802.3/3 70210 वा HDBT टाइप 70210 PD डिजाइन गर्दै • AN193: PD1/PD2 प्रयोग गरी एक प्रकार 802.3/70100 IEEE 70200at/af संचालित यन्त्र फ्रन्ट एन्ड डिजाइन गर्दै |

माइक्रोचिप Webसाइट

माइक्रोचिपले हाम्रो मार्फत अनलाइन समर्थन प्रदान गर्दछ webसाइट मा www.microchip.com/। यो webसाइट बनाउन प्रयोग गरिन्छ files र जानकारी सजिलै ग्राहकहरु लाई उपलब्ध छ। उपलब्ध सामग्री मध्ये केही समावेश:

- उत्पादन समर्थन - डाटा पाना र इरेटा, आवेदन नोटहरू र sample प्रोग्रामहरू, डिजाइन स्रोतहरू, प्रयोगकर्ताको गाइड र हार्डवेयर समर्थन कागजातहरू, नवीनतम सफ्टवेयर रिलीजहरू र अभिलेख गरिएको सफ्टवेयर

- सामान्य प्राविधिक समर्थन - बारम्बार सोधिने प्रश्नहरू (FAQs), प्राविधिक समर्थन अनुरोधहरू, अनलाइन छलफल समूहहरू, माइक्रोचिप डिजाइन साझेदार कार्यक्रम सदस्य सूची

- माइक्रोचिपको व्यवसाय - उत्पादन चयनकर्ता र अर्डर गाइडहरू, नवीनतम माइक्रोचिप प्रेस विज्ञप्ति, सेमिनार र घटनाहरूको सूची, माइक्रोचिप बिक्री कार्यालयहरूको सूची, वितरक र कारखाना प्रतिनिधिहरू

उत्पादन परिवर्तन सूचना सेवा

माइक्रोचिपको उत्पादन परिवर्तन सूचना सेवाले ग्राहकहरूलाई माइक्रोचिप उत्पादनहरूमा अद्यावधिक राख्न मद्दत गर्दछ। कुनै निर्दिष्ट उत्पादन परिवार वा रुचिको विकास उपकरणसँग सम्बन्धित परिवर्तनहरू, अद्यावधिकहरू, संशोधनहरू वा त्रुटिहरू हुँदा सदस्यहरूले इमेल सूचना प्राप्त गर्नेछन्।

दर्ता गर्न, जानुहोस् www.microchip.com/pcn र दर्ता निर्देशनहरू पालना गर्नुहोस्।

ग्राहक समर्थन

माइक्रोचिप उत्पादनका प्रयोगकर्ताहरूले धेरै च्यानलहरू मार्फत सहायता प्राप्त गर्न सक्छन्:

- वितरक वा प्रतिनिधि

- स्थानीय बिक्री कार्यालय

- इम्बेडेड समाधान इन्जिनियर (ESE)

- प्राविधिक समर्थन

ग्राहकहरूले समर्थनको लागि आफ्नो वितरक, प्रतिनिधि वा ESE लाई सम्पर्क गर्नुपर्छ। स्थानीय बिक्री कार्यालयहरू पनि ग्राहकहरूलाई मद्दत गर्न उपलब्ध छन्। यस कागजातमा बिक्री कार्यालय र स्थानहरूको सूची समावेश गरिएको छ। मार्फत प्राविधिक सहयोग उपलब्ध छ webसाइट मा: www.microchip.com/support

माइक्रोचिप उपकरण कोड सुरक्षा सुविधा

माइक्रोचिप उपकरणहरूमा कोड सुरक्षा सुविधाको निम्न विवरणहरू नोट गर्नुहोस्:

- माइक्रोचिप उत्पादनहरू तिनीहरूको विशेष माइक्रोचिप डेटा पानामा समावेश विनिर्देशहरू पूरा गर्छन्।

- Microchip विश्वास गर्दछ कि यसको उत्पादनहरूको परिवार आज बजारमा आफ्नो प्रकारको सबैभन्दा सुरक्षित परिवारहरू मध्ये एक हो, जब इच्छित रूपमा र सामान्य अवस्थामा प्रयोग गरिन्छ।

- कोड सुरक्षा सुविधा उल्लङ्घन गर्न प्रयोग गरिने बेइमान र सम्भवतः अवैध तरिकाहरू छन्। यी सबै विधिहरू, हाम्रो ज्ञानमा, माइक्रोचिपको डेटा पानाहरूमा समावेश सञ्चालन विनिर्देशहरू बाहिरको रूपमा माइक्रोचिप उत्पादनहरू प्रयोग गर्न आवश्यक छ। सम्भवतः, त्यसो गर्ने व्यक्ति बौद्धिक सम्पत्तिको चोरीमा संलग्न छ।

- Microchip ग्राहकसँग काम गर्न इच्छुक छ जो आफ्नो कोडको अखण्डताको बारेमा चिन्तित छन्।

- न त माइक्रोचिप वा कुनै अन्य अर्धचालक निर्माताले तिनीहरूको कोडको सुरक्षाको ग्यारेन्टी गर्न सक्छ। कोड सुरक्षाको मतलब यो होइन कि हामीले उत्पादनलाई "अनब्रेक्बल" भनी ग्यारेन्टी दिइरहेका छौं।

कोड सुरक्षा निरन्तर विकसित हुँदैछ। हामी माइक्रोचिपमा हाम्रा उत्पादनहरूको कोड सुरक्षा सुविधाहरू निरन्तर सुधार गर्न प्रतिबद्ध छौं। माइक्रोचिपको कोड सुरक्षा सुविधा तोड्ने प्रयास डिजिटल मिलेनियम प्रतिलिपि अधिकार ऐनको उल्लङ्घन हुन सक्छ। यदि त्यस्ता कार्यहरूले तपाइँको सफ्टवेयर वा अन्य प्रतिलिपि अधिकार कार्यमा अनाधिकृत पहुँचलाई अनुमति दिन्छ भने, तपाइँसँग त्यो ऐन अन्तर्गत राहतको लागि मुद्दा हाल्ने अधिकार हुन सक्छ।

कानूनी सूचना

यस प्रकाशनमा यन्त्र एप्लिकेसनहरू र त्यस्ता कुराहरू सम्बन्धी जानकारी समावेश गरिएको जानकारी केवल तपाइँको सुविधाको लागि प्रदान गरिएको छ र अद्यावधिकहरू द्वारा हटाइएको हुन सक्छ। यो सुनिश्चित गर्न को लागी तपाइँको जिम्मेवारी हो कि तपाइँको आवेदन तपाइँको विशिष्टताहरु संग मिल्छ। MICROCHIP ले कुनै पनि प्रकारको कुनै प्रतिनिधित्व वा वारेन्टी गर्दैन चाहे अभिव्यक्त होस् वा निहित, लिखित वा मौखिक, वैधानिक वा अन्यथा, जानकारीसँग सम्बन्धित, MICROCHIP सम्बन्धी, अनुमतिरहित, गैर-सम्बन्धित, सीमितता सहित। माइक्रोचिपले यो जानकारी र यसको प्रयोगबाट उत्पन्न हुने सबै दायित्वलाई अस्वीकार गर्दछ। जीवन समर्थन र/वा सुरक्षा अनुप्रयोगहरूमा माइक्रोचिप उपकरणहरूको प्रयोग पूर्ण रूपमा क्रेताको जोखिममा हुन्छ, र क्रेता कुनै पनि र सबै क्षतिहरू, दावीहरू, सूटहरू, वा त्यस्ता प्रयोगबाट हुने खर्चहरूबाट हानिरहित माइक्रोचिपको रक्षा गर्न, क्षतिपूर्ति गर्न र होल्ड गर्न सहमत हुन्छन्। कुनै पनि माइक्रोचिप बौद्धिक सम्पदा अधिकार अन्तर्गत कुनै पनि इजाजतपत्र, अस्पष्ट वा अन्यथा, अन्यथा भनिएको छैन।

ट्रेडमार्कहरू

माइक्रोचिपको नाम र लोगो, माइक्रोचिप लोगो, Adaptec, AnyRate, AVR, AVR लोगो, AVR Freaks, Bes Time, Bit Cloud, chip KIT, chip KIT लोगो, Crypto Memory, Crypto RF, ds PIC, Flash Flex, Flex PWR, HELDO, IGLOO, Jukebox, Kilo, Kleber, LAN Check, Link MD, maX Stylus, maX Touch, Media LB, मेगा AVR, माइक्रो सेमी, माइक्रो सेमी लोगो, MOST, MOST लोगो, MPLAB, Opto Lyzer, PackerTime, PIC, pico Power, PICSTART, PIC32 लोगो, Polar Fire, Prochip Designer, QTouch, SAM-BA, Sen Genuity, SpyNIC, SST, SST लोगो, SuperFlash, Symmetricom, Sync Server, Tachyon, Temp Trackr, TimeSource, tinyAVR, UNI/O, Vectron , र XMEGA संयुक्त राज्य अमेरिका र अन्य देशहरूमा माइक्रोचिप टेक्नोलोजीको दर्ता ट्रेडमार्कहरू हुन्।

APT, ClockWorks, The Embedded Control Solutions Company, Ether Synch, Flash Tec, हाइपर स्पीड कन्ट्रोल, हाइपर लाइट लोड, Bintelli MOS, Libero, motor Bench, touch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, Pro ASIC Plus लोगो, Quiet-Wire, SmartFusion, Sync World, Timex, Time Cesium, Time Hub, Time Pictra, TimeProvider, Vite, WinPath, र ZL संयुक्त राज्य अमेरिका मा माइक्रोचिप टेक्नोलोजी को दर्ता ट्रेडमार्क हो।

आसन्न कुञ्जी दमन, AKS, एनालग-फर-द-डिजिटल उमेर, कुनै पनि क्यापेसिटर, कुनै पनि भित्र, कुनै पनि बाहिर, ब्लू स्काई, बडी कम, कोड गार्ड, क्रिप्टो प्रमाणीकरण, क्रिप्टो अटोमोटिभ, क्रिप्टो कम्प्यानियन, क्रिप्टो नियन्त्रक, मसालेदार, सीडीईएम नेट। , डायनामिक औसत मिलान, DAM, ECAN, Ether GREEN, इन-सर्किट सिरियल प्रोग्रामिङ, ICSP, INI Cnet, इन्टर-चिप कनेक्टिभिटी, जिटर ब्लकर, क्लेबर नेट, क्लेबर नेट लोगो, मेम ब्रेन, मिन्डी, Mi Wi, MPASM, MPF, MPLAB प्रमाणित लोगो, MPLIB, MPLINK, Multi TRAK, Net Detach, Omniscient Code Generation, PICDEM, PICDEM.net, PI चिट, PI टेल, पावर स्मार्ट, शुद्ध सिलिकन, म्याट्रिक्स, REAL ICE, Ripple Blocker, SAM-ICE, सिरियल क्वाड I/O, SMART-IS, SQI, Super Switcher, Super Switcher II, Total Endurance, TSHARC, USB चेक, Vary Sense, View स्प्यान, वाइपर लक, वायरलेस DNA, र ZENA संयुक्त राज्य अमेरिका र अन्य देशहरूमा माइक्रोचिप टेक्नोलोजीको ट्रेडमार्कहरू हुन्।

SQTP संयुक्त राज्य अमेरिका मा माइक्रोचिप टेक्नोलोजी को एक सेवा चिन्ह हो

Adaptec लोगो, फ्रिक्वेन्सी अन डिमान्ड, सिलिकन स्टोरेज टेक्नोलोजी, र Symmcom अन्य देशहरूमा माइक्रोचिप टेक्नोलोजी इन्कका दर्ता ट्रेडमार्क हुन्।

GestIC माइक्रोचिप टेक्नोलोजी जर्मनी II GmbH & Co. KG को दर्ता गरिएको ट्रेडमार्क हो, माइक्रोचिप टेक्नोलोजी इन्कको सहायक कम्पनी, अन्य देशहरूमा।

यहाँ उल्लेख गरिएका अन्य सबै ट्रेडमार्कहरू तिनीहरूको सम्बन्धित कम्पनीहरूको सम्पत्ति हुन्।

© 2022, Microchip Technology Incorporated, USA मा छापिएको, सबै अधिकार सुरक्षित।

ISBN: 978-1-6683-0205-7

गुणस्तर व्यवस्थापन प्रणाली

माइक्रोचिपको गुणस्तर व्यवस्थापन प्रणालीको बारेमा जानकारीको लागि, कृपया भ्रमण गर्नुहोस् www.microchip.com/quality.

विश्वव्यापी बिक्री र सेवा

कर्पोरेट कार्यालय

2355 West Chandler Blvd।

Chandler, AZ 85224-6199

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९

प्राविधिक समर्थन: www.microchip.com/support

Web ठेगाना: www.microchip.com

© 2022 माइक्रोचिप टेक्नोलोजी इंक।

र यसको सहायक आवेदन नोट

DS00003468B

कागजातहरू / स्रोतहरू

|

MICROCHIP AN3468 HDBaseT प्रकार 3 संचालित यन्त्र फ्रन्ट-एन्ड [pdf] मालिकको म्यानुअल AN3468 HDBaseT प्रकार 3 संचालित यन्त्र फ्रन्ट-एन्ड, AN3468, HDBaseT प्रकार 3 संचालित यन्त्र फ्रन्ट-एन्ड, संचालित यन्त्र फ्रन्ट-एन्ड, फ्रन्ट-एन्ड |