माइक्रोचिप PIC24 फ्लैश प्रोग्रामिंग

उत्पादन जानकारी

फ्ल्यास प्रोग्रामिङ

यन्त्रहरूको dsPIC33/PIC24 परिवारहरूसँग प्रयोगकर्ता कोडको कार्यान्वयनको लागि आन्तरिक प्रोग्रामयोग्य फ्ल्यास प्रोग्राम मेमोरी छ। यो मेमोरी प्रोग्राम गर्न तीनवटा तरिकाहरू छन्:

- तालिका निर्देशन सञ्चालन

- इन-सर्किट सिरियल प्रोग्रामिङ (ICSP)

- इन-एप्लिकेशन प्रोग्रामिङ (IAP)

तालिका निर्देशनहरूले फ्ल्याश प्रोग्राम मेमोरी स्पेस र dsPIC33/PIC24 यन्त्रहरूको डेटा मेमोरी स्पेस बीच डेटा स्थानान्तरण गर्ने विधि प्रदान गर्दछ। TBLRDL निर्देशन बिट्स [१५:०] प्रोग्राम मेमोरी स्पेसबाट पढ्न प्रयोग गरिन्छ। TBLWTL निर्देशन फ्ल्यास कार्यक्रम मेमोरी स्पेसको बिट [१५:०] मा लेख्न प्रयोग गरिन्छ। TBLRDL र TBLWTL वर्ड मोड वा बाइट मोडमा फ्ल्यास कार्यक्रम मेमोरी पहुँच गर्न सक्छ।

फ्ल्यास कार्यक्रम मेमोरी ठेगानाको अतिरिक्त, तालिका निर्देशनले W दर्ता (वा मेमोरी स्थानको लागि एक W दर्ता सूचक) पनि निर्दिष्ट गर्दछ, जुन फ्ल्यास प्रोग्राम मेमोरी डेटाको स्रोत हो, वा फ्ल्यास प्रोग्रामको लागि गन्तव्य। मेमोरी पढियो।

यो खण्डले फ्ल्यास कार्यक्रम मेमोरी प्रोग्रामिङको लागि प्रविधिको वर्णन गर्दछ। उपकरणहरूको dsPIC33/ PIC24 परिवारहरूसँग प्रयोगकर्ता कोडको कार्यान्वयनको लागि आन्तरिक प्रोग्रामयोग्य फ्ल्यास प्रोग्राम मेमोरी छ। यो मेमोरी प्रोग्राम गर्न तीनवटा तरिकाहरू छन्:

- रन-टाइम सेल्फ-प्रोग्रामिङ (RTSP)

- इन-सर्किट सिरियल प्रोग्रामिङ™ (ICSP™)

- एन्हान्स्ड इन-सर्किट सिरियल प्रोग्रामिङ (EICSP)

RTSP कार्यान्वयनको क्रममा एप्लिकेसन सफ्टवेयरद्वारा गरिन्छ, जबकि ICSP र EICSP बाह्य प्रोग्रामरबाट यन्त्रमा सिरियल डेटा जडान प्रयोग गरेर प्रदर्शन गरिन्छ। ICSP र EICSP ले RTSP भन्दा धेरै छिटो प्रोग्रामिङ समय अनुमति दिन्छ। RTSP प्रविधिहरू खण्ड 4.0 "रन-टाइम सेल्फ-प्रोग्रामिङ (RTSP)" मा वर्णन गरिएको छ। ICSP र EICSP प्रोटोकलहरू सम्बन्धित उपकरणहरूको लागि प्रोग्रामिङ विशिष्टता कागजातहरूमा परिभाषित छन्, जुन माइक्रोचिपबाट डाउनलोड गर्न सकिन्छ। webसाइट (http://www.microchip.com)। C भाषामा प्रोग्रामिङ गर्दा, फ्ल्यास प्रोग्रामिङलाई सहज बनाउने धेरै बिल्ट-इन प्रकार्यहरू उपलब्ध हुन्छन्। बिल्ट-इन प्रकार्यहरू बारे विवरणहरूको लागि "MPLAB® XC16 C कम्पाइलर प्रयोगकर्ताको गाइड" (DS50002071) हेर्नुहोस्।

उत्पादन उपयोग निर्देशन

फ्ल्यास कार्यक्रम मेमोरी प्रोग्राम गर्न, यी चरणहरू पालना गर्नुहोस्:

- तपाईंले प्रयोग गरिरहनुभएको यन्त्रलाई पारिवारिक सन्दर्भ म्यानुअल खण्डले समर्थन गर्छ कि गर्दैन भनी जाँच गर्न यन्त्र डेटा पानामा हेर्नुहोस्।

- माइक्रोचिप विश्वव्यापीबाट उपकरण डेटा पाना र पारिवारिक सन्दर्भ पुस्तिका खण्डहरू डाउनलोड गर्नुहोस् Webसाइट मा: http://www.microchip.com.

- मेमोरी (तालिका निर्देशन सञ्चालन, इन-सर्किट सिरियल प्रोग्रामिङ (ICSP), इन-एप्लिकेशन प्रोग्रामिङ (IAP)) प्रोग्राम गर्नका लागि तीनवटा विधिहरू मध्ये एउटा छनोट गर्नुहोस्।

- यदि तालिका निर्देशन सञ्चालन प्रयोग गर्दै हुनुहुन्छ भने, प्रोग्राम मेमोरी स्पेसको बिटहरू [१५:०] पढ्नको लागि TBLRDL निर्देशन प्रयोग गर्नुहोस् र फ्ल्यास प्रोग्राम मेमोरी स्पेसको बिटहरू[15:0] मा लेख्न TBLWTL निर्देशन प्रयोग गर्नुहोस्।

- फ्ल्यास प्रोग्राम मेमोरी डेटाको स्रोतको रूपमा W दर्ता (वा मेमोरी स्थानको लागि W दर्ता सूचक) निर्दिष्ट गर्न निश्चित गर्नुहोस्, वा फ्ल्यास कार्यक्रम मेमोरी पढ्नको लागि गन्तव्य।

फ्ल्यास कार्यक्रम मेमोरी प्रोग्रामिङमा थप जानकारी र विवरणहरूको लागि, dsPIC33/PIC24 पारिवारिक सन्दर्भ पुस्तिका हेर्नुहोस्।

तालिका निर्देशन सञ्चालन

तालिका निर्देशनहरूले फ्ल्याश प्रोग्राम मेमोरी स्पेस र dsPIC33/PIC24 यन्त्रहरूको डेटा मेमोरी स्पेस बीच डेटा स्थानान्तरण गर्ने विधि प्रदान गर्दछ। यो खण्डले फ्ल्यास कार्यक्रम मेमोरीको प्रोग्रामिङको क्रममा प्रयोग गरिएका तालिका निर्देशनहरूको सारांश प्रदान गर्दछ। त्यहाँ चार आधारभूत तालिका निर्देशनहरू छन्:

- TBLRDL: तालिका कम पढ्नुहोस्

- TBLRDH: तालिका उच्च पढ्नुहोस्

- TBLWTL: तालिका कम लेख्नुहोस्

- TBLWTH: तालिका उच्च लेख्नुहोस्

TBLRDL निर्देशन बिट्स [१५:०] प्रोग्राम मेमोरी स्पेसबाट पढ्न प्रयोग गरिन्छ। TBLWTL निर्देशन फ्ल्यास कार्यक्रम मेमोरी स्पेसको बिट [१५:०] मा लेख्न प्रयोग गरिन्छ। TBLRDL र TBLWTL वर्ड मोड वा बाइट मोडमा फ्ल्यास कार्यक्रम मेमोरी पहुँच गर्न सक्छ।

TBLRDH र TBLWTH निर्देशनहरू प्रोग्राम मेमोरी स्पेसको बिटहरू [२३:१६] पढ्न वा लेख्न प्रयोग गरिन्छ। TBLRDH र TBLWTH वर्ड वा बाइट मोडमा फ्ल्यास कार्यक्रम मेमोरी पहुँच गर्न सक्छ। किनभने फ्ल्याश कार्यक्रम मेमोरी मात्र 23 बिट चौडा छ, TBLRDH र TBLWTH निर्देशनहरूले फ्ल्यास प्रोग्राम मेमोरीको माथिल्लो बाइटलाई सम्बोधन गर्न सक्छ जुन अवस्थित छैन। यो बाइटलाई "फ्यान्टम बाइट" भनिन्छ। फ्यान्टम बाइटको कुनै पनि पढाइले ०x०० फर्काउनेछ। प्रेत बाइटमा लेख्ने कुनै प्रभाव छैन। 16-बिट फ्ल्यास प्रोग्राम मेमोरीलाई दुई छेउ-छेउ 24-बिट स्पेसको रूपमा मान्न सकिन्छ, प्रत्येक स्पेसले समान ठेगाना दायरा साझा गर्दछ। तसर्थ, TBLRDL र TBLWTL निर्देशनहरू "कम" प्रोग्राम मेमोरी स्पेस (PM[0:00]) पहुँच गर्दछ। TBLRDH र TBLWTH निर्देशनहरूले "उच्च" कार्यक्रम मेमोरी स्पेस (PM[24:16]) पहुँच गर्दछ। PM[15:0] लाई कुनै पनि पढ्ने वा लेख्नेले फ्यान्टम (अप्रवर्तनीय) बाइट पहुँच गर्नेछ। जब कुनै पनि तालिका निर्देशनहरू बाइट मोडमा प्रयोग गरिन्छ, तालिका ठेगानाको न्यूनतम महत्त्वपूर्ण बिट (LSb) बाइट चयन बिटको रूपमा प्रयोग गरिनेछ। LSb ले उच्च वा कम कार्यक्रम मेमोरी स्पेसमा कुन बाइट पहुँच गरिन्छ निर्धारण गर्दछ।

चित्र 2-1 ले फ्ल्यास प्रोग्राम मेमोरीलाई तालिका निर्देशनहरू प्रयोग गरेर कसरी सम्बोधन गरिन्छ भनेर वर्णन गर्दछ। 24-बिट कार्यक्रम मेमोरी ठेगाना TBLPAG रजिष्टरको बिटहरू [7:0] र तालिका निर्देशनमा निर्दिष्ट W दर्ताबाट प्रभावकारी ठेगाना (EA) प्रयोग गरेर बनाइन्छ। 24-बिट प्रोग्राम काउन्टर (पीसी) सन्दर्भको लागि चित्र 2-1 मा चित्रण गरिएको छ। EA को माथिल्लो 23 बिट फ्ल्यास कार्यक्रम मेमोरी स्थान चयन गर्न प्रयोग गरिन्छ।

बाइट मोड तालिका निर्देशनहरूको लागि, 16-बिट फ्ल्यास प्रोग्राम मेमोरी शब्दको कुन बाइटलाई सम्बोधन गरिएको छ भनेर चयन गर्न W दर्ता EA को LSb प्रयोग गरिन्छ; '1' ले बिट्स चयन गर्दछ[15:8] र '0' ले बिट्स चयन गर्दछ[7:0]। वर्ड मोडमा तालिका निर्देशनको लागि W दर्ता EA को LSb लाई बेवास्ता गरिएको छ। फ्ल्यास कार्यक्रम मेमोरी ठेगानाको अतिरिक्त, तालिका निर्देशनले W दर्ता (वा मेमोरी स्थानको लागि एक W दर्ता सूचक) पनि निर्दिष्ट गर्दछ, जुन फ्ल्यास प्रोग्राम मेमोरी डेटाको स्रोत हो, वा फ्ल्यास प्रोग्रामको लागि गन्तव्य। मेमोरी पढियो। बाइट मोडमा तालिका लेखन सञ्चालनको लागि, स्रोत कार्य दर्ताको बिटहरू [१५:८] बेवास्ता गरिन्छ।

तालिका पढ्ने निर्देशनहरू प्रयोग गर्दै

तालिका पढ्न दुई चरणहरू आवश्यक छ:

- ठेगाना सूचक TBLPAG दर्ता र W दर्ताहरू मध्ये एक प्रयोग गरेर सेटअप गरिएको छ।

- ठेगाना स्थानमा फ्ल्यास कार्यक्रम मेमोरी सामग्रीहरू पढ्न सकिन्छ।

- वर्ड मोड पढ्नुहोस्

Ex मा देखाइएको कोडample 2-1 र Example 2-2 ले वर्ड मोडमा तालिका निर्देशनहरू प्रयोग गरेर फ्ल्यास प्रोग्राम मेमोरीको शब्द कसरी पढ्ने भनेर देखाउँछ।

- बाइट मोड पढ्नुहोस्

Ex मा देखाइएको कोडample 2-3 ले कम बाइटको पढाइमा पोस्ट-इन्क्रिमेन्ट अपरेटर देखाउँछ, जसले कार्य दर्ताको ठेगानालाई एकले वृद्धि गर्छ। यसले तेस्रो लेखन निर्देशनमा मध्य बाइटमा पहुँचको लागि EA[0] लाई '1' मा सेट गर्छ। पछिल्लो पोस्ट-वृद्धिले W0 लाई अर्को फ्ल्यास कार्यक्रम मेमोरी स्थानमा औंल्याउँदै समान ठेगानामा सेट गर्छ।

- टेबल राइट ल्याचहरू

तालिका लेखन निर्देशनहरू सिधै nonvolatile कार्यक्रम मेमोरीमा लेख्दैनन्। यसको सट्टा, तालिका लेखन निर्देशनहरू लोड राइट ल्याचहरू जसले लेखन डाटा भण्डारण गर्दछ। NVM ठेगाना दर्ताहरू पहिलो ठेगानाको साथ लोड हुनुपर्छ जहाँ latched डाटा लेखिएको हुनुपर्छ। जब सबै लेखन ल्याचहरू लोड हुन्छन्, वास्तविक मेमोरी प्रोग्रामिङ सञ्चालन निर्देशनहरूको विशेष अनुक्रम कार्यान्वयन गरेर सुरु हुन्छ। प्रोग्रामिङको बखत, हार्डवेयरले राइट ल्याचमा भएको डाटालाई फ्ल्यास मेमोरीमा स्थानान्तरण गर्छ। लेखन ल्याचहरू सधैं ठेगाना 0xFA0000 मा सुरु हुन्छ, र शब्द प्रोग्रामिङका लागि 0xFA0002 मार्फत विस्तार हुन्छ, वा पङ्क्ति प्रोग्रामिङ भएका यन्त्रहरूका लागि 0xFA00FE मार्फत विस्तार हुन्छ।

नोट: लेखन ल्याचहरूको संख्या उपकरण अनुसार भिन्न हुन्छ। उपलब्ध लेखन ल्याचहरूको संख्याको लागि निर्दिष्ट उपकरण डेटा पानाको "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्।

नियन्त्रण दर्ताहरू

फ्ल्यास कार्यक्रम मेमोरी इरेज र लेखन कार्यहरू प्रोग्राम गर्न धेरै विशेष प्रकार्य दर्ताहरू (SFRs) प्रयोग गरिन्छ: NVMCON, NVMKEY, र NVM ठेगाना दर्ताहरू, NVMADR र NVMADRU।

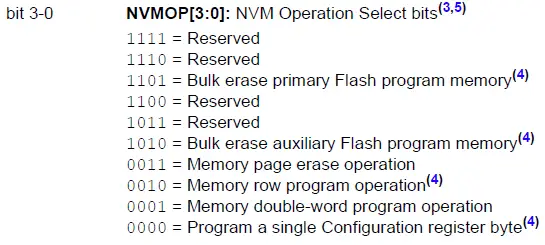

NVMCON दर्ता

NVMCON दर्ता फ्ल्यास र कार्यक्रम/मेटाउने कार्यहरूको लागि प्राथमिक नियन्त्रण दर्ता हो। यो दर्ताले मेटाउने वा कार्यक्रम सञ्चालन गर्ने वा कार्यक्रम सुरु गर्ने वा मेटाउने चक्र चयन गर्छ। NVMCON दर्ता दर्ता ३-१ मा देखाइएको छ। NVMCON को तल्लो बाइटले NVM सञ्चालनको प्रकार कन्फिगर गर्दछ जुन प्रदर्शन गरिनेछ।

NVMKEY दर्ता

NVMKEY दर्ता (रेजिस्टर 3-4 हेर्नुहोस्) फ्ल्यास मेमोरी भ्रष्ट गर्न सक्ने NVMCON को आकस्मिक लेखहरू रोक्न प्रयोग गरिने लेख्ने मात्र दर्ता हो। एक पटक अनलक भएपछि, NVMCON मा लेख्नलाई एउटा निर्देशन चक्रको लागि अनुमति दिइन्छ जसमा WR बिटलाई मेटाउन वा कार्यक्रम दिनचर्या सुरु गर्न सेट गर्न सकिन्छ। समय आवश्यकताहरू दिई, अवरोधहरू असक्षम गर्न आवश्यक छ।

मेटाउने वा प्रोग्रामिङ अनुक्रम सुरु गर्न निम्न चरणहरू पूरा गर्नुहोस्:

- अवरोधहरू असक्षम गर्नुहोस्।

- NVMKEY मा 0x55 लेख्नुहोस्।

- NVMKEY मा 0xAA लेख्नुहोस्।

- WR बिट (NVMCON[15]) सेट गरेर प्रोग्रामिङ लेखन चक्र सुरु गर्नुहोस्।

- दुई NOP निर्देशनहरू कार्यान्वयन गर्नुहोस्।

- अवरोधहरू पुनर्स्थापित गर्नुहोस्।

अवरोधहरू असक्षम गर्दै

सफल नतिजा सुनिश्चित गर्नका लागि सबै फ्ल्यास अपरेशनहरूको लागि अवरोधहरू असक्षम पार्नु आवश्यक छ। यदि NVMKEY अनलक अनुक्रमको समयमा अवरोध उत्पन्न हुन्छ भने, यसले WR बिटमा लेख्न रोक लगाउन सक्छ। खण्ड 3.2 "NVMKEY दर्ता" मा छलफल गरिए अनुसार, NVMKEY अनलक अनुक्रम कुनै अवरोध बिना कार्यान्वयन हुनुपर्छ।

ग्लोबल इन्टरप्ट इनेबल (GIE बिट) असक्षम गरेर वा DISI निर्देशन प्रयोग गरेर दुई मध्ये एउटा विधिमा अवरोधहरू असक्षम गर्न सकिन्छ। DISI निर्देशन सिफारिस गरिएको छैन किनकि यसले प्राथमिकता 6 वा तलका अवरोधहरूलाई मात्र असक्षम गर्दछ; त्यसैले, ग्लोबल इन्टरप्ट सक्षम विधि प्रयोग गर्नुपर्छ।

CPU ले GIE लाई कोड प्रवाहलाई असर गर्नु अघि दुई निर्देशन चक्रहरू लिन्छ। दुई NOP निर्देशनहरू पछि आवश्यक छ, वा कुनै अन्य उपयोगी काम निर्देशनहरू, जस्तै NVMKEY लोड गर्दै प्रतिस्थापन गर्न सकिन्छ; यो सेट र स्पष्ट सञ्चालन दुवै लागू हुन्छ। अवरोधहरू पुन: सक्षम गर्दा सावधानी अपनाउनु पर्छ ताकि NVM लक्षित दिनचर्याले अवरोधहरूलाई अनुमति दिँदैन जब अघिल्लो भनिने प्रकार्यले तिनीहरूलाई अन्य कारणहरूको लागि असक्षम पारेको छ। यसलाई विधानसभामा सम्बोधन गर्न, GIE बिटको अवस्था कायम राख्न स्ट्याक पुश र पप प्रयोग गर्न सकिन्छ। C मा, RAM मा एक चर GIE खाली गर्नु अघि INTCON2 भण्डारण गर्न प्रयोग गर्न सकिन्छ। अवरोधहरू असक्षम गर्न निम्न अनुक्रम प्रयोग गर्नुहोस्:

- स्ट्याकमा INTCON2 पुश गर्नुहोस्।

- GIE बिट खाली गर्नुहोस्।

- दुई NOP वा NVMKEY लाई लेख्नुहोस्।

- WR बिट (NVMCON[15]) सेट गरेर प्रोग्रामिङ चक्र सुरु गर्नुहोस्।

- INTCON2 को POP द्वारा GIE स्थिति पुनर्स्थापित गर्नुहोस्।

NVM ठेगाना दर्ताहरू

दुई NVM ठेगाना रजिष्टरहरू, NVMADRU र NVMADR, जब सम्मिलित हुन्छन्, चयन गरिएको पङ्क्तिको 24-बिट EA वा प्रोग्रामिङ सञ्चालनका लागि शब्द बनाउँछन्। NVMADRU दर्ता EA को माथिल्लो आठ बिटहरू समात्न प्रयोग गरिन्छ, र NVMADR दर्ता EA को तल्लो 16 बिटहरू समात्न प्रयोग गरिन्छ। केही यन्त्रहरूले यी समान दर्ताहरूलाई NVMADRL र NVMADRH को रूपमा सन्दर्भ गर्न सक्छन्। NVM ठेगाना दर्ताहरूले सधैं दोहोरो निर्देशन शब्दको सीमालाई दोहोरो निर्देशन शब्द प्रोग्रामिङ सञ्चालन गर्दा, पङ्क्ति प्रोग्रामिङ सञ्चालन गर्दा पङ्क्तिको सीमा वा पृष्ठ मेटाउने कार्य सञ्चालन गर्दा पृष्ठ सीमालाई संकेत गर्नुपर्छ।

दर्ता 3-1: NVMCON: फ्ल्यास मेमोरी नियन्त्रण दर्ता

नोट

- यो बिट पावर अन रिसेट (POR) मा मात्र रिसेट गर्न सकिन्छ (अर्थात, खाली)।

- निष्क्रिय मोडबाट बाहिर निस्कँदा, फ्ल्यास कार्यक्रम मेमोरी सञ्चालन हुनु अघि त्यहाँ पावर-अप ढिलाइ (TVREG) हुन्छ। थप जानकारीको लागि विशेष यन्त्र डेटा पानाको "विद्युतीय विशेषताहरू" अध्यायलाई सन्दर्भ गर्नुहोस्।

- NVMOP [3:0] को अन्य सबै संयोजनहरू लागू नगरिएका छन्।

- यो कार्यक्षमता सबै उपकरणहरूमा उपलब्ध छैन। उपलब्ध अपरेशनहरूको लागि निर्दिष्ट उपकरण डेटा पानामा "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्।

- PWRSAV निर्देशनहरू कार्यान्वयन गरेपछि पावर-बचत मोडमा प्रवेश सबै विचाराधीन NVM सञ्चालनहरू पूरा गर्न आकस्मिक छ।

- यो बिट RAM बफर गरिएको पङ्क्ति प्रोग्रामिङ समर्थन गर्ने उपकरणहरूमा मात्र उपलब्ध छ। उपलब्धताको लागि यन्त्र-विशिष्ट डेटा पानालाई सन्दर्भ गर्नुहोस्।

नोट

- यो बिट पावर अन रिसेट (POR) मा मात्र रिसेट गर्न सकिन्छ (अर्थात, खाली)।

- निष्क्रिय मोडबाट बाहिर निस्कँदा, फ्ल्यास कार्यक्रम मेमोरी सञ्चालन हुनु अघि त्यहाँ पावर-अप ढिलाइ (TVREG) हुन्छ। थप जानकारीको लागि विशेष यन्त्र डेटा पानाको "विद्युतीय विशेषताहरू" अध्यायलाई सन्दर्भ गर्नुहोस्।

- NVMOP [3:0] को अन्य सबै संयोजनहरू लागू नगरिएका छन्।

- यो कार्यक्षमता सबै उपकरणहरूमा उपलब्ध छैन। उपलब्ध अपरेशनहरूको लागि निर्दिष्ट उपकरण डेटा पानामा "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्।

- PWRSAV निर्देशनहरू कार्यान्वयन गरेपछि पावर-बचत मोडमा प्रवेश सबै विचाराधीन NVM सञ्चालनहरू पूरा गर्न आकस्मिक छ।

- यो बिट RAM बफर गरिएको पङ्क्ति प्रोग्रामिङ समर्थन गर्ने उपकरणहरूमा मात्र उपलब्ध छ। उपलब्धताको लागि यन्त्र-विशिष्ट डेटा पानालाई सन्दर्भ गर्नुहोस्।

दर्ता ३-२: NVMADRU: Nonvolatile मेमोरी माथिल्लो ठेगाना दर्ता

3-3 दर्ता गर्नुहोस्: NVMADR: Nonvolatile मेमोरी ठेगाना दर्ता

दर्ता 3-4: NVMKEY: Nonvolatile मेमोरी कुञ्जी दर्ता

रन-टाइम सेल्फ-प्रोग्रामिङ (RTSP)

RTSP ले प्रयोगकर्ता अनुप्रयोगलाई फ्ल्यास कार्यक्रम मेमोरी सामग्री परिमार्जन गर्न अनुमति दिन्छ। RTSP TBLRD (टेबल रिड) र TBLWT (टेबल राइट) निर्देशनहरू, TBLPAG दर्ता, र NVM नियन्त्रण दर्ताहरू प्रयोग गरेर पूरा गरिएको छ। RTSP को साथ, प्रयोगकर्ता अनुप्रयोगले फ्ल्यास मेमोरीको एक पृष्ठ मेटाउन सक्छ र केहि उपकरणहरूमा दुई निर्देशन शब्दहरू वा 128 निर्देशन शब्दहरू प्रोग्राम गर्न सक्छ।

RTSP सञ्चालन

dsPIC33/PIC24 फ्लैश कार्यक्रम मेमोरी एरेलाई मेटाउने पृष्ठहरूमा व्यवस्थित गरिएको छ जसमा 1024 निर्देशनहरू सम्म हुन सक्छन्। डबल-वर्ड प्रोग्रामिङ विकल्प dsPIC33/PIC24 परिवारहरूमा सबै यन्त्रहरूमा उपलब्ध छ। थप रूपमा, केहि उपकरणहरूसँग पङ्क्ति प्रोग्रामिङ क्षमता छ, जसले एक पटकमा 128 निर्देशन शब्दहरूको प्रोग्रामिङलाई अनुमति दिन्छ। प्रोग्रामिङ र मेटाउने कार्यहरू सधैं एक समान डबल प्रोग्रामिङ शब्द, पङ्क्ति वा पृष्ठ सीमाहरूमा हुन्छ। प्रोग्रामिङ पङ्क्तिको उपलब्धता र साइजहरू र मेटाउनको लागि पृष्ठ आकारको लागि निर्दिष्ट उपकरण डेटा पानाको "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्। फ्ल्यास प्रोग्राम मेमोरीले होल्डिङ बफरहरू लागू गर्दछ, जसलाई राइट ल्याच भनिन्छ, जसमा यन्त्रको आधारमा प्रोग्रामिङ डेटाको 128 निर्देशनहरू समावेश हुन सक्छ। वास्तविक प्रोग्रामिङ सञ्चालन गर्नु अघि, लेखन डाटा लेखन ल्याचहरूमा लोड हुनुपर्छ। RTSP को लागि आधारभूत अनुक्रम तालिका सूचक, TBLPAG दर्ता, र त्यसपछि लेखन ल्याचहरू लोड गर्न TBLWT निर्देशनहरूको श्रृंखला प्रदर्शन गर्नु हो। NVMCON दर्तामा नियन्त्रण बिटहरू सेट गरेर प्रोग्रामिङ गरिन्छ। लेखन ल्याचहरू लोड गर्न आवश्यक TBLWTL र TBLWTH निर्देशनहरूको संख्या लेख्नु पर्ने प्रोग्राम शब्दहरूको संख्या बराबर छ।

नोट: यो सिफारिस गरिन्छ कि TBLPAG दर्ता परिमार्जन गर्नु अघि बचत गर्नुहोस् र प्रयोग पछि पुनर्स्थापित गर्नुहोस्।

सावधान

केही यन्त्रहरूमा, कन्फिगरेसन बिटहरू कार्यक्रमको अन्तिम पृष्ठमा फ्ल्यास प्रयोगकर्ता मेमोरी स्पेसमा "फ्ल्याश कन्फिगरेसन बाइट्स" भनिने खण्डमा भण्डारण गरिन्छ। यी उपकरणहरूसँग, कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्य प्रदर्शन गर्दा फ्ल्यास कन्फिगरेसन बाइटहरू मेटिन्छ, जसले कोड सुरक्षा सक्षम गर्दछ। त्यसैले, प्रयोगकर्ताहरूले कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्यहरू प्रदर्शन गर्नु हुँदैन। यो चिन्ताको विषय होइन जब कन्फिगरेसन बिटहरू कन्फिगरेसन मेमोरी स्पेसमा "उपकरण कन्फिगरेसन दर्ताहरू" भनिन्छ। कन्फिगरेसन बिटहरू कहाँ छन् भनी निर्धारण गर्नको लागि निर्दिष्ट यन्त्र डेटा पानाको "मेमोरी संगठन" अध्यायमा कार्यक्रम मेमोरी नक्सालाई सन्दर्भ गर्नुहोस्।

फ्ल्यास प्रोग्रामिङ सञ्चालन

प्रोग्रामिंग वा RTSP मोडमा आन्तरिक फ्ल्यास कार्यक्रम मेमोरी मेटाउनको लागि प्रोग्राम वा मेटाउने अपरेशन आवश्यक छ। कार्यक्रम वा मेटाउने कार्य स्वचालित रूपमा उपकरण द्वारा समयबद्ध हुन्छ (समय जानकारीको लागि विशिष्ट उपकरण डेटा पानालाई सन्दर्भ गर्नुहोस्)। WR बिट सेट गर्दै (NVMCON[15]) सञ्चालन सुरु हुन्छ। सञ्चालन समाप्त भएपछि WR बिट स्वचालित रूपमा खाली हुन्छ। प्रोग्रामिङ सञ्चालन समाप्त नभएसम्म CPU स्टलहरू। CPU ले यस समयमा कुनै पनि निर्देशनहरू कार्यान्वयन गर्दैन वा अवरोधहरूलाई प्रतिक्रिया दिने छैन। यदि प्रोग्रामिङ चक्रमा कुनै अवरोधहरू देखा पर्छन् भने, तिनीहरू चक्र पूरा नभएसम्म पेन्डिङ रहनेछन्। केही dsPIC33/PIC24 यन्त्रहरूले सहायक फ्ल्यास कार्यक्रम मेमोरी प्रदान गर्न सक्छन् (विवरणका लागि विशिष्ट यन्त्र डेटा पानाको "मेमोरी संगठन" अध्यायलाई सन्दर्भ गर्नुहोस्), जसले प्रयोगकर्ता फ्ल्यास कार्यक्रम मेमोरी मेटाइने र/वा प्रोग्राम गरिएको बेला CPU स्टलहरू बिना निर्देशन कार्यान्वयन गर्न अनुमति दिन्छ। यसको विपरीत, सहायक फ्ल्यास प्रोग्राम मेमोरी सीपीयू स्टलहरू बिना प्रोग्राम गर्न सकिन्छ, जबसम्म कोड प्रयोगकर्ता फ्ल्यास प्रोग्राम मेमोरीबाट कार्यान्वयन गरिन्छ। NVM अवरोध प्रोग्रामिङ सञ्चालन पूरा भएको संकेत गर्न प्रयोग गर्न सकिन्छ।

नोट

- RTSP मेटाउने वा प्रोग्रामिङ सञ्चालन भइरहेको बेला POR वा BOR घटना भयो भने, RTSP सञ्चालन तुरुन्तै रद्द हुन्छ। यन्त्र रिसेटबाट बाहिर आएपछि प्रयोगकर्ताले पुन: RTSP सञ्चालनलाई कार्यान्वयन गर्नुपर्छ।

- यदि एक EXTR, SWR, WDTO, TRAPR, CM वा IOPUWR रिसेट घटना हुन्छ जब RTSP मेटाउने वा प्रोग्रामिङ कार्य प्रगतिमा छ भने, RTSP सञ्चालन पूरा भएपछि मात्र उपकरण रिसेट हुनेछ।

RTSP प्रोग्रामिङ एल्गोरिदम

यो खण्डले RTSP प्रोग्रामिङको वर्णन गर्दछ, जसमा तीनवटा प्रमुख प्रक्रियाहरू हुन्छन्।

परिमार्जन गर्न डाटा पृष्ठको RAM छवि सिर्जना गर्दै

परिमार्जन गर्न डाटा पृष्ठको RAM छवि सिर्जना गर्न यी दुई चरणहरू प्रदर्शन गर्नुहोस्:

- फ्ल्यास प्रोग्राम मेमोरीको पृष्ठ पढ्नुहोस् र डाटा "इमेज" को रूपमा डाटा RAM मा भण्डार गर्नुहोस्। RAM छवि पृष्ठ ठेगाना सीमाबाट सुरु गरेर पढ्नु पर्छ।

- आवश्यकता अनुसार RAM डाटा छवि परिमार्जन गर्नुहोस्।

फ्ल्यास कार्यक्रम मेमोरी मेटाउँदै

माथिको चरण 1 र 2 पूरा गरेपछि, फ्ल्यास कार्यक्रम मेमोरी पृष्ठ मेटाउन निम्न चार चरणहरू गर्नुहोस्:

- चरण 3 बाट पढिएको फ्ल्यास कार्यक्रम मेमोरीको पृष्ठ मेटाउन NVMOP[0:3] बिट्स (NVMCON [0:1]) सेट गर्नुहोस्।

- NVMADRU र NMVADR दर्ताहरूमा मेटिने पृष्ठको सुरु ठेगाना लेख्नुहोस्।

- अवरोधहरू असक्षम पारिएको छ:

- a) WR बिट सेटिङ सक्षम गर्न NVMKEY दर्तामा कुञ्जी अनुक्रम लेख्नुहोस् (NVMCON[15])।

- b) WR बिट सेट गर्नुहोस्; यसले मेटाउने चक्र सुरु गर्नेछ।

- c) दुई NOP निर्देशनहरू कार्यान्वयन गर्नुहोस्।

- मेटाउने चक्र पूरा भएपछि WR बिट खाली हुन्छ।

फ्ल्यास मेमोरी पृष्ठ प्रोग्राम गर्दै

प्रक्रियाको अर्को भाग फ्ल्यास मेमोरी पृष्ठ प्रोग्राम गर्नु हो। फ्ल्यास मेमोरी पृष्ठलाई चरण 1 मा सिर्जना गरिएको छविबाट डेटा प्रयोग गरेर प्रोग्राम गरिएको छ। डेटालाई दोहोरो निर्देशन शब्दहरू वा पङ्क्तिहरूको वृद्धिमा लेखन ल्याचहरूमा स्थानान्तरण गरिन्छ। सबै उपकरणहरूमा डबल निर्देशन शब्द प्रोग्रामिङ क्षमता छ। (यदि, र कस्तो प्रकारको, पङ्क्ति प्रोग्रामिङ उपलब्ध छ भनी निर्धारण गर्नको लागि विशेष यन्त्र डेटा पानामा "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्।) राइट ल्याचहरू लोड भएपछि, प्रोग्रामिङ सञ्चालन सुरु हुन्छ, जसले डाटा ट्रान्सफर गर्छ। फ्ल्यास मेमोरीमा ल्याचहरू लेख्नुहोस्। सम्पूर्ण पृष्ठ प्रोग्राम गरिएको नभएसम्म यो दोहोर्याइएको छ। निम्न तीन चरणहरू दोहोर्याउनुहोस्, फ्ल्यास पृष्ठको पहिलो निर्देशन शब्दबाट सुरु गर्दै र सम्पूर्ण पृष्ठ प्रोग्राम नभएसम्म दोहोरो प्रोग्राम शब्दहरू, वा निर्देशन पङ्क्तिहरूको चरणहरूमा वृद्धि गर्दै:

- लेखन ल्याचहरू लोड गर्नुहोस्:

- a) TBLPAG रेजिस्टरलाई लेख्ने लचहरूको स्थानमा देखाउन सेट गर्नुहोस्।

- b) TBLWTL र TBLWTH निर्देशनहरूको जोडी प्रयोग गरेर ल्याचहरूको इच्छित संख्या लोड गर्नुहोस्:

- डबल-वर्ड प्रोग्रामिङको लागि, TBLWTL र TBLWTH निर्देशनहरूको दुई जोडी आवश्यक छ

- पङ्क्ति प्रोग्रामिङको लागि, प्रत्येक निर्देशन शब्द पङ्क्ति तत्वको लागि TBLWTL र TBLWTH निर्देशनहरूको एक जोडी आवश्यक छ।

- प्रोग्रामिङ सञ्चालन सुरु गर्नुहोस्:

- क) NVMOP[3:0] बिटहरू (NVMCON[3:0]) सेट गर्नुहोस् कि त दोहोरो निर्देशन शब्दहरू वा एक निर्देशन पङ्क्ति, उपयुक्त भएमा प्रोग्राम गर्न।

ख) NVMADRU र NVMADR दर्ताहरूमा प्रोग्राम गरिनु पर्ने दोहोरो निर्देशन शब्द वा निर्देशन पङ्क्तिको पहिलो ठेगाना लेख्नुहोस्।

ग) अवरोधहरू असक्षम पारिएको छ:

• WR बिट सेटिङ सक्षम गर्न NVMKEY दर्तामा कुञ्जी अनुक्रम लेख्नुहोस् (NVMCON[15])

• WR बिट सेट गर्नुहोस्; यसले मेटाउने चक्र सुरु गर्नेछ

• दुई NOP निर्देशनहरू कार्यान्वयन गर्नुहोस्

- क) NVMOP[3:0] बिटहरू (NVMCON[3:0]) सेट गर्नुहोस् कि त दोहोरो निर्देशन शब्दहरू वा एक निर्देशन पङ्क्ति, उपयुक्त भएमा प्रोग्राम गर्न।

- प्रोग्रामिङ चक्र पूरा भएपछि WR बिट खाली हुन्छ।

फ्ल्यास कार्यक्रम मेमोरीको इच्छित मात्रा प्रोग्राम गर्न आवश्यक अनुसार सम्पूर्ण प्रक्रिया दोहोर्याउनुहोस्।

नोट

- प्रयोगकर्ताले याद राख्नु पर्छ कि RTSP प्रयोग गरेर मेटाउन सकिने फ्ल्यास कार्यक्रम मेमोरीको न्यूनतम मात्रा एक सिङ्ग मेटिएको पृष्ठ हो। त्यसकारण, यो महत्त्वपूर्ण छ कि यी स्थानहरूको छविलाई सामान्य उद्देश्य RAM मा भण्डारण गरिएको छ मेटाउने चक्र सुरु हुनु अघि।

- फ्ल्यास प्रोग्राम मेमोरीमा पङ्क्ति वा शब्द मेटाइनु अघि दुई पटक भन्दा बढी प्रोग्राम गर्नु हुँदैन।

- फ्ल्यासको अन्तिम पृष्ठमा भण्डारण गरिएका कन्फिगरेसन बाइटहरू भएका यन्त्रहरूमा, कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्यले कन्फिगरेसन बाइटहरू खाली गर्छ, जसले कोड सुरक्षालाई सक्षम बनाउँछ। यी उपकरणहरूमा, फ्ल्यास मेमोरीको अन्तिम पृष्ठ मेटाउनु हुँदैन।

फ्ल्यासको एउटा पृष्ठ मेटाउँदै

पूर्वमा देखाइएको कोड अनुक्रमample 4-1 लाई फ्ल्यास प्रोग्राम मेमोरीको पृष्ठ मेटाउन प्रयोग गर्न सकिन्छ। NVMCON दर्ता कार्यक्रम मेमोरीको एक पृष्ठ मेटाउन कन्फिगर गरिएको छ। NVMADR र NMVADRU दर्ताहरू मेटिने पृष्ठको सुरु ठेगानाको साथ लोड हुन्छन्। कार्यक्रम मेमोरी "सम" पृष्ठ ठेगाना सीमामा मेटिएको हुनुपर्छ। फ्ल्यास पृष्ठको साइज निर्धारण गर्नको लागि विशिष्ट उपकरण डेटा पानाको "फ्ल्याश प्रोग्राम मेमोरी" अध्याय हेर्नुहोस्।

WR बिट (NVMCON[15]) सेट गर्नु अघि NVMKEY दर्तामा विशेष अनलक, वा कुञ्जी अनुक्रम लेखेर मेटाउने कार्य सुरु गरिएको छ। अनलक अनुक्रम सही क्रममा कार्यान्वयन गर्न आवश्यक छ, जस्तै पूर्व मा देखाइएको छample 4-1, बिना अवरोध; त्यसैले, अवरोधहरू असक्षम हुनुपर्छ।

मेटाउने चक्र पछि कोडमा दुई NOP निर्देशनहरू सम्मिलित गर्नुपर्छ। केहि उपकरणहरूमा, कन्फिगरेसन बिटहरू कार्यक्रम फ्ल्यासको अन्तिम पृष्ठमा भण्डारण गरिन्छ। यी यन्त्रहरूसँग, कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्य प्रदर्शन गर्दा फ्ल्यास कन्फिगरेसन बाइटहरू मेटिन्छ, परिणाम स्वरूप कोड सुरक्षा सक्षम पार्दै। प्रयोगकर्ताहरूले कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्यहरू प्रदर्शन गर्नु हुँदैन।

ल्याचहरू लोड गर्दै

राइट ल्याचहरू प्रयोगकर्ता एप्लिकेसन टेबल राइट र वास्तविक प्रोग्रामिङ अनुक्रम बीच भण्डारण संयन्त्रको रूपमा प्रयोग गरिन्छ। प्रोग्रामिङ सञ्चालनको क्रममा, यन्त्रले राइट ल्याचबाट डाटालाई फ्ल्यास मेमोरीमा स्थानान्तरण गर्नेछ। पङ्क्ति प्रोग्रामिङलाई समर्थन गर्ने यन्त्रहरूका लागि, Example 4-3 ले निर्देशनहरूको अनुक्रम देखाउँछ जुन 128 लिखित लचहरू लोड गर्न प्रयोग गर्न सकिन्छ (128 निर्देशन शब्दहरू)। 128 TBLWTL र 128 TBLWTH निर्देशनहरू फ्ल्यास प्रोग्राम मेमोरीको पङ्क्ति प्रोग्रामिङको लागि राइट ल्याचहरू लोड गर्न आवश्यक छ। तपाइँको यन्त्रमा उपलब्ध प्रोग्रामिङ ल्याचहरूको संख्या निर्धारण गर्न विशेष यन्त्र डेटा पानाको "फ्ल्याश प्रोग्राम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्। पङ्क्ति प्रोग्रामिङलाई समर्थन नगर्ने यन्त्रहरूका लागि, Example 4-4 ले निर्देशनहरूको अनुक्रम देखाउँछ जुन दुई लेखन ल्याचहरू लोड गर्न प्रयोग गर्न सकिन्छ (दुई निर्देशन शब्दहरू)। दुई TBLWTL र दुई TBLWTH निर्देशनहरू लेखन ल्याचहरू लोड गर्न आवश्यक छ।

नोट

- Load_Write_Latch_Row को लागि कोड Ex मा देखाइएको छample 4-3 र Load_Write_Latch_Word को लागि कोड Ex मा देखाइएको छampले 4-4। यी दुवैमा कोड पूर्वampलेसलाई पछिको पूर्वमा उल्लेख गरिएको छampलेस।

- ल्याचहरूको संख्याको लागि निर्दिष्ट उपकरण डेटा पानालाई सन्दर्भ गर्नुहोस्।

एकल पङ्क्ति प्रोग्रामिङ पूर्वAMPLE

NVMCON दर्ता फ्ल्यास कार्यक्रम मेमोरीको एक पङ्क्ति प्रोग्राम गर्न कन्फिगर गरिएको छ। WR बिट (NVMCON[15]) सेट गर्नु अघि NVMKEY दर्तामा विशेष अनलक, वा कुञ्जी अनुक्रम लेखेर कार्यक्रम सञ्चालन सुरु गरिएको छ। अनलक अनुक्रम कुनै अवरोध बिना कार्यान्वयन गर्न आवश्यक छ, र सटीक क्रम मा, Ex मा देखाइएको छ।ampले 4-5। त्यसैले, अनुक्रम लेख्नु अघि अवरोधहरू असक्षम हुनुपर्छ।

नोट: सबै यन्त्रहरूमा पङ्क्ति प्रोग्रामिङ क्षमता हुँदैन। यो विकल्प उपलब्ध छ कि छैन भनेर निर्धारण गर्नको लागि निर्दिष्ट उपकरण डेटा पानाको "फ्ल्याश कार्यक्रम मेमोरी" अध्यायलाई सन्दर्भ गर्नुहोस्।

प्रोग्रामिङ चक्र पछि कोडमा दुई NOP निर्देशनहरू सम्मिलित गर्नुपर्छ।

र्याम बफर प्रयोग गरी पङ्क्ति प्रोग्रामिङ

चयन गर्नुहोस् dsPIC33 यन्त्रहरूले पङ्क्ति प्रोग्रामिङलाई डेटा RAM मा बफर स्पेसबाट सीधा प्रदर्शन गर्न अनुमति दिन्छ, TBLWT निर्देशनहरूसँग डेटा स्थानान्तरण गर्न होल्डिङ ल्याचहरू मार्फत जानुको सट्टा। RAM बफरको स्थान NVMSRCADR दर्ता (हरू) द्वारा निर्धारण गरिन्छ, जुन डेटा RAM ठेगानामा भरिएको हुन्छ जसमा प्रोग्राम डेटाको पहिलो शब्द लेखिनेछ।

कार्यक्रम सञ्चालन गर्नु अघि, RAM मा बफर स्पेस प्रोग्राम गरिएको डेटाको पङ्क्तिसँग लोड हुनुपर्छ। RAM लाई संकुचित (प्याक गरिएको) वा असम्पीडित ढाँचामा लोड गर्न सकिन्छ। कम्प्रेस गरिएको भण्डारणले दुई नजिकका कार्यक्रम डेटा शब्दहरूको सबैभन्दा महत्त्वपूर्ण बाइटहरू (MSBs) भण्डारण गर्न एक डेटा शब्द प्रयोग गर्दछ। असम्पीडित ढाँचाले प्रत्येक प्रोग्राम डेटा शब्दको लागि दुई डेटा शब्दहरू प्रयोग गर्दछ, प्रत्येक अन्य शब्दको माथिल्लो बाइट 00h हुन्छ। कम्प्रेस गरिएको ढाँचाले असंपीडित ढाँचाको तुलनामा डेटा RAM मा लगभग 3/4 ठाउँ प्रयोग गर्दछ। असम्पीडित ढाँचा, अर्कोतर्फ, 24-बिट प्रोग्राम डेटा शब्दको संरचनाको नक्कल गर्दछ, माथिल्लो फ्यान्टम बाइटसँग पूरा हुन्छ। डाटा ढाँचा RPDF बिट (NVMCON[9]) द्वारा चयन गरिएको छ। यी दुई ढाँचाहरू चित्र 4-1 मा देखाइएको छ।

र्याम बफर लोड भएपछि, फ्ल्याश ठेगाना पोइन्टर्स, NVMADR र NVMADRU, फ्ल्यास पङ्क्तिको 24-बिट सुरु ठेगाना लेख्नको लागि लोड हुन्छन्। राइट ल्याचहरू प्रोग्रामिङको रूपमा, प्रक्रिया NVM अनलक अनुक्रम लेखेर सुरु गरिन्छ, त्यसपछि WR बिट सेट गरेर। एकचोटि प्रारम्भ भएपछि, यन्त्रले स्वचालित रूपमा सही ल्याचहरू लोड गर्दछ र सबै बाइटहरू प्रोग्राम नगरेसम्म NVM ठेगाना दर्ता गर्दछ। उदाहरणample 4-7 ले पूर्व देखाउँछampप्रक्रिया को ले। यदि NVMSRCADR लाई मानमा सेट गरिएको छ जसमा डेटा अन्डररन त्रुटि अवस्था उत्पन्न हुन्छ भने, URERR बिट (NVMCON[8]) सर्त संकेत गर्न सेट गरिनेछ।

RAM बफर पङ्क्ति प्रोग्रामिङ लागू गर्ने उपकरणहरूले पनि एक वा दुई ल्याचहरू लागू गर्दछ। यी TBLWT निर्देशनहरू प्रयोग गरेर लोड गरिएका छन् र शब्द प्रोग्रामिङ सञ्चालनहरू गर्न प्रयोग गरिन्छ।

वर्ड प्रोग्रामिङ

NVMCON दर्ता फ्ल्यास कार्यक्रम मेमोरीको दुई निर्देशन शब्दहरू प्रोग्राम गर्न कन्फिगर गरिएको छ। WR बिट (NVMCON[15]) सेट गर्नु अघि NVMKEY दर्तामा विशेष अनलक, वा कुञ्जी अनुक्रम लेखेर कार्यक्रम सञ्चालन सुरु गरिएको छ। अनलक अनुक्रम सही क्रममा कार्यान्वयन गर्न आवश्यक छ, जस्तै पूर्व मा देखाइएको छample 4-8, बिना अवरोध। त्यसैले, अनुक्रम लेख्नु अघि अवरोधहरू असक्षम हुनुपर्छ।

प्रोग्रामिङ चक्र पछि कोडमा दुई NOP निर्देशनहरू सम्मिलित गर्नुपर्छ।

यन्त्र कन्फिगरेसन दर्ताहरूमा लेख्दै

केहि यन्त्रहरूमा, कन्फिगरेसन बिटहरू "उपकरण कन्फिगरेसन दर्ताहरू" भनिने खण्डमा कन्फिगरेसन मेमोरी स्पेसमा भण्डारण गरिन्छ। अन्य उपकरणहरूमा, कन्फिगरेसन बिटहरू "फ्ल्याश कन्फिगरेसन बाइट्स" नामक खण्डमा फ्ल्यास प्रयोगकर्ता मेमोरी स्पेसको अन्तिम पृष्ठमा भण्डारण गरिन्छ। यी उपकरणहरूसँग, कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्य प्रदर्शन गर्दा फ्ल्यास कन्फिगरेसन बाइटहरू मेटिन्छ, जसले कोड सुरक्षा सक्षम गर्दछ। त्यसैले, प्रयोगकर्ताहरूले कार्यक्रम मेमोरीको अन्तिम पृष्ठमा पृष्ठ मेटाउने कार्यहरू प्रदर्शन गर्नु हुँदैन। कन्फिगरेसन बिटहरू कहाँ छन् भनी निर्धारण गर्नको लागि निर्दिष्ट यन्त्र डेटा पानाको "मेमोरी संगठन" अध्यायमा कार्यक्रम मेमोरी नक्सालाई सन्दर्भ गर्नुहोस्।

जब कन्फिगरेसन बिटहरू कन्फिगरेसन मेमोरी स्पेसमा भण्डारण गरिन्छ, RTSP लाई उपकरण कन्फिगरेसन दर्ताहरूमा लेख्न प्रयोग गर्न सकिन्छ, र RTSP ले प्रत्येक कन्फिगरेसन दर्तालाई पहिले मेटाउने चक्र प्रदर्शन नगरी व्यक्तिगत रूपमा पुन: लेख्न अनुमति दिन्छ। कन्फिगरेसन दर्ताहरू लेख्दा सावधानी अपनाउनु पर्छ किनभने तिनीहरूले प्रणाली घडी स्रोत, PLL र WDT सक्षम जस्ता महत्वपूर्ण यन्त्र अपरेटिङ प्यारामिटरहरू नियन्त्रण गर्छन्।

यन्त्र कन्फिगरेसन दर्ताको लागि प्रोग्रामिङको प्रक्रिया फ्ल्यास प्रोग्राम मेमोरी प्रोग्रामिङको लागि प्रक्रिया जस्तै छ, बाहेक केवल TBLWTL निर्देशनहरू आवश्यक छ। यो किनभने प्रत्येक उपकरण कन्फिगरेसन दर्तामा माथिल्लो आठ बिटहरू प्रयोग नगरिएका छन्। यसबाहेक, कन्फिगरेसन दर्ताहरू पहुँच गर्न तालिका लेखन ठेगानाको बिट 23 सेट हुनुपर्छ। "dsPIC70000618/PIC33 पारिवारिक सन्दर्भ पुस्तिका" मा "डिवाइस कन्फिगरेसन" (DS24) र यन्त्र कन्फिगरेसन दर्ताहरूको पूर्ण विवरणको लागि विशेष यन्त्र डेटा पानामा "विशेष सुविधाहरू" अध्यायलाई सन्दर्भ गर्नुहोस्।

नोट

- यन्त्र कन्फिगरेसन रेजिस्टरहरूमा लेख्ने सबै उपकरणहरूमा उपलब्ध छैन। यन्त्र-विशिष्ट NVMOP [३:०] बिट्सको परिभाषा अनुसार उपलब्ध मोडहरू निर्धारण गर्न विशेष यन्त्र डेटा पानामा "विशेष सुविधाहरू" अध्यायलाई सन्दर्भ गर्नुहोस्।

- यन्त्र कन्फिगरेसन रेजिस्टरहरूमा RTSP प्रदर्शन गर्दा, यन्त्रले आन्तरिक FRC ओसिलेटर (PLL बिना) प्रयोग गरी काम गरिरहेको हुनुपर्छ। यदि यन्त्र फरक घडी स्रोतबाट सञ्चालन भइरहेको छ भने, यन्त्र कन्फिगरेसन दर्ताहरूमा RTSP सञ्चालन गर्नु अघि आन्तरिक FRC ओसिलेटर (NOSC[2:0] = 000) मा घडी स्विच गर्नुपर्छ।

- यदि प्राथमिक ओसिलेटर मोड चयन बिटहरू (POSCMD[1:0]) Oscillator कन्फिगरेसन दर्ता (FOSC) मा नयाँ मानमा पुन: प्रोग्राम गरिएको छ भने, प्रयोगकर्ताले घडी स्विचिङ मोड बिटहरू (FCKSM[1:0]) मा सुनिश्चित गर्नुपर्छ। FOSC दर्ताको प्रारम्भिक प्रोग्राम गरिएको मान '0' हुन्छ, यो RTSP सञ्चालन गर्नु अघि।

कन्फिगरेसन दर्ता एल्गोरिदम लेख्नुहोस्

सामान्य प्रक्रिया निम्नानुसार छ:

- TBLWTL निर्देशन प्रयोग गरेर तालिकामा नयाँ कन्फिगरेसन मान लेख्नुहोस्।

- कन्फिगरेसन दर्ता राइटको लागि NVMCON कन्फिगर गर्नुहोस् (NVMCON = 0x4000)।

- NVMADRU र NVMADR दर्ताहरूमा प्रोग्राम गर्नको लागि कन्फिगरेसन दर्ताको ठेगाना लेख्नुहोस्।

- यदि सक्षम छ भने, अवरोधहरू असक्षम गर्नुहोस्।

- NVMKEY दर्तामा कुञ्जी अनुक्रम लेख्नुहोस्।

- WR बिट (NVMCON[15]) सेट गरेर लेखन अनुक्रम सुरु गर्नुहोस्।

- यदि आवश्यक भएमा अवरोधहरू पुन: सक्षम गर्नुहोस्।

Example 4-10 ले कोड अनुक्रम देखाउँछ जुन उपकरण कन्फिगरेसन दर्ता परिमार्जन गर्न प्रयोग गर्न सकिन्छ।

नक्सा दर्ता गर्नुहोस्

फ्ल्यास प्रोग्रामिङसँग सम्बन्धित दर्ताहरूको सारांश तालिका ५-१ मा प्रदान गरिएको छ।

यो खण्डले म्यानुअलको यस खण्डसँग सम्बन्धित अनुप्रयोग नोटहरू सूचीबद्ध गर्दछ। यी एप्लिकेसन नोटहरू dsPIC33/PIC24 उत्पादन परिवारहरूको लागि विशेष रूपमा लेखिएको नहुन सक्छ, तर अवधारणाहरू सान्दर्भिक छन् र परिमार्जन र सम्भावित सीमितताहरूसँग प्रयोग गर्न सकिन्छ। फ्ल्यास प्रोग्रामिङसँग सम्बन्धित हालको एप्लिकेसन नोटहरू निम्न हुन्:

नोट: कृपया माइक्रोचिप भ्रमण गर्नुहोस् webसाइट (www.microchip.com) अतिरिक्त आवेदन नोटहरू र कोड पूर्वको लागिampउपकरणहरूको dsPIC33/PIC24 परिवारहरूको लागि।

संशोधन इतिहास

संशोधन A (अगस्ट 2009)

यो यस कागजातको प्रारम्भिक जारी संस्करण हो।

संशोधन B (फेब्रुअरी 2011)

यस संशोधनले निम्न अद्यावधिकहरू समावेश गर्दछ:

- Examples:

- हटाइयो पूर्वample 5-3 र Examp5 4 XNUMX००-XNUMX०

- अद्यावधिक गरिएको पूर्वampले ४-५, उदाample 4-5 र Examp4 10 XNUMX००-XNUMX०

- #WR को कुनै पनि सन्दर्भहरू पूर्वमा #15 मा अद्यावधिक गरियोampले ४-५, उदाample 4-5 र Examp4 8 XNUMX००-XNUMX०

- Ex मा निम्न अपडेट गरियोampले ४-३:

- शीर्षक "वर्ड प्रोग्रामिङ" लाई "पङ्क्ति प्रोग्रामिङका लागि ल्याचहरू लोड गर्दै" मा अद्यावधिक गरियो

- #ram_image को कुनै पनि सन्दर्भ #0xFA मा अद्यावधिक गरिएको थियो

- Ex थप्नुभयोamp4 4 XNUMX००-XNUMX०

- मा शीर्षक अद्यावधिक गर्नुभयोamp4 8 XNUMX००-XNUMX०

- नोट:

- खण्ड 4.2 "फ्ल्याश प्रोग्रामिङ सञ्चालन" मा दुई टिप्पणीहरू थपियो

- खण्ड 4.5.2 "लोडिङ ल्याचहरू" मा टिप्पणी अद्यावधिक गरियो

- खण्ड 4.6 "उपकरण कन्फिगरेसन दर्ताहरूमा लेख्ने" मा तीनवटा टिप्पणीहरू थपियो

- तालिका ५-१ मा नोट १ थपियो

- दर्ताहरू:

- NVMOP[3:0] का लागि बिट मानहरू अद्यावधिक गरियो: फ्ल्यास मेमोरी कन्ट्रोल (NVMCON) दर्तामा NVM सञ्चालन बिट्स चयन गर्नुहोस् (रेजिस्टर ३-१ हेर्नुहोस्)

- खण्डहरू:

- हटाइएको खण्ड ५.२.१.४ "शब्द मोड लेख्नुहोस्" र ५.२.१.५ "बाइट मोड लेख्नुहोस्"

- खण्ड 3.0 "नियन्त्रण दर्ताहरू" अद्यावधिक गरियो

- खण्ड 4.5.5 "वर्ड प्रोग्रामिङ" मा निम्न अद्यावधिक गरिएको छ:

- खण्ड शीर्षक "फ्ल्यास मेमोरीको एक शब्द प्रोग्रामिङ" लाई "वर्ड प्रोग्रामिङ" मा परिवर्तन गरियो

- पहिलो अनुच्छेद अपडेट गरियो

- दोस्रो अनुच्छेदमा "एक शब्द" लाई "शब्दहरूको जोडी" मा परिवर्तन गरियो

- खण्ड 1 मा नयाँ चरण 4.6.1 थपियो "कन्फिगरेसन दर्ता एल्गोरिथ्म लेख्नुहोस्"

- तालिकाहरू:

- अपडेट गरिएको तालिका ५-१

- कार्यक्रम मेमोरीका केही सन्दर्भहरू फ्ल्यास कार्यक्रम मेमोरीमा अद्यावधिक गरियो

- अन्य साना अद्यावधिकहरू जस्तै भाषा र ढाँचा अपडेटहरू कागजातभरि समावेश गरिएको थियो

संशोधन C (जुन २०११)

यस संशोधनले निम्न अद्यावधिकहरू समावेश गर्दछ:

- Examples:

- अद्यावधिक गरिएको पूर्वamp4 1 XNUMX००-XNUMX०

- अद्यावधिक गरिएको पूर्वamp4 8 XNUMX००-XNUMX०

- नोट:

- खण्ड 4.1 "RTSP सञ्चालन" मा एउटा टिप्पणी थपियो

- खण्ड 3 "फ्ल्यास प्रोग्रामिङ सञ्चालन" मा टिप्पणी 4.2 थपियो

- खण्ड 3 "RTSP प्रोग्रामिङ एल्गोरिदम" मा टिप्पणी 4.2.1 थपियो

- खण्ड 4.5.1 "फ्ल्यासको एक पृष्ठ मेटाउँदै" मा एउटा टिप्पणी थपियो

- खण्ड 2 मा नोट 4.5.2 थपियो "लेखन ल्याचहरू लोड गर्दै"

- दर्ताहरू:

- Nonvolatile मेमोरी ठेगाना दर्तामा बिट्स 15-0 को लागि बिट विवरण अद्यावधिक गरियो (दर्ता 3-3 हेर्नुहोस्)

- खण्डहरू:

- खण्ड 4.1 "RTSP सञ्चालन" अद्यावधिक गरियो

- अपडेट गरिएको खण्ड ४.५.५ "शब्द प्रोग्रामिङ"

- अन्य साना अद्यावधिकहरू जस्तै भाषा र ढाँचा अपडेटहरू कागजातभरि समावेश गरिएको थियो

संशोधन D (डिसेम्बर 2011)

यस संशोधनले निम्न अद्यावधिकहरू समावेश गर्दछ:

- खण्ड २.१.३ "तालिका लेख्ने लचहरू" अद्यावधिक गरिएको

- खण्ड 3.2 "NVMKEY दर्ता" अपडेट गरिएको

- NVMCON मा नोटहरू अद्यावधिक गरियो: फ्ल्यास मेमोरी नियन्त्रण दर्ता (दर्ता 3-1 हेर्नुहोस्)

- खण्ड 4.0 "रन-टाइम सेल्फ-प्रोग्रामिङ (RTSP)" भरि व्यापक अद्यावधिकहरू बनाइयो।

- अन्य साना अद्यावधिकहरू जस्तै भाषा र ढाँचा अपडेटहरू कागजातभरि समावेश गरिएको थियो

संशोधन E (अक्टोबर 2018)

यस संशोधनले निम्न अद्यावधिकहरू समावेश गर्दछ:

- Ex थप्नुभयोampले ४-५, उदाampले ४-५, उदाample 4-6 र Examp4 9 XNUMX००-XNUMX०

- खण्ड 4.5.4 "RAM बफर प्रयोग गरेर पङ्क्ति प्रोग्रामिङ" थपियो

- अद्यावधिक गरिएको खण्ड 1.0 "परिचय", खण्ड 3.3 "NVM ठेगाना दर्ताहरू", खण्ड 4.0 "रन-टाइम सेल्फ-प्रोग्रामिङ (RTSP)" र खण्ड 4.5.3 "एकल पङ्क्ति प्रोग्रामिङ पूर्वampले "

- अपडेट गरिएको दर्ता 3-1

- अद्यावधिक गरिएको पूर्वamp4 7 XNUMX००-XNUMX०

- अपडेट गरिएको तालिका ५-१

संशोधन F (नोभेम्बर २०२१)

खण्ड 3.2.1 "अवरोधहरू असक्षम गर्दै" थपियो।

अद्यावधिक गरिएको पूर्वampले ४-५, उदाampले ४-५, उदाampले ४-५, उदाampले ४-५, उदाampले ४-५, उदाampले ४-५, उदाampले ४-५, उदाample 4-9 र Exampले 4-10।

खण्ड 3.2 “NVMKEY दर्ता”, खण्ड 4.5.1 “फ्ल्यासको एउटा पृष्ठ मेटाउँदै”, खण्ड 4.5.3 “एकल पङ्क्ति प्रोग्रामिङ पूर्व” अपडेट गरिएकोample" र खण्ड 4.6.1 "कन्फिगरेसन दर्ता एल्गोरिदम लेख्नुहोस्"।

माइक्रोचिप उत्पादनहरूमा कोड सुरक्षा सुविधाको निम्न विवरणहरू नोट गर्नुहोस्:

- माइक्रोचिप उत्पादनहरूले तिनीहरूको विशेष माइक्रोचिप डेटा पानामा समावेश विशिष्टताहरू पूरा गर्दछ।

- Microchip ले विश्वास गर्छ कि यसको उत्पादनहरु को परिवार सुरक्षित छ जब अभिप्रेत तरिकामा प्रयोग गरिन्छ, सञ्चालन विनिर्देशहरु भित्र, र सामान्य अवस्थामा।

- माइक्रोचिप मान र आक्रामक रूपमा यसको बौद्धिक सम्पत्ति अधिकारहरूको रक्षा गर्दछ। माइक्रोचिप उत्पादनको कोड सुरक्षा सुविधाहरू उल्लङ्घन गर्ने प्रयासहरू कडा रूपमा निषेध गरिएको छ र डिजिटल मिलेनियम प्रतिलिपि अधिकार ऐन उल्लङ्घन गर्न सक्छ।

- न त माइक्रोचिप वा कुनै अन्य अर्धचालक निर्माताले यसको कोडको सुरक्षाको ग्यारेन्टी गर्न सक्छ। कोड सुरक्षाको मतलब यो होइन कि हामीले उत्पादन "अनब्रेक्बल" छ भनेर ग्यारेन्टी गरिरहेका छौं। कोड सुरक्षा निरन्तर विकसित हुँदैछ। Microchip हाम्रा उत्पादनहरूको कोड सुरक्षा सुविधाहरू निरन्तर सुधार गर्न प्रतिबद्ध छ

यो प्रकाशन र यहाँको जानकारी माइक्रोचिप उत्पादनहरूमा मात्र प्रयोग गर्न सकिन्छ, डिजाइन, परीक्षण, र माइक्रोचिप उत्पादनहरू तपाईंको अनुप्रयोगसँग एकीकृत गर्न सहित। कुनै पनि अन्य तरिकामा यो जानकारीको प्रयोगले यी सर्तहरूको उल्लङ्घन गर्दछ। यन्त्र अनुप्रयोगहरू सम्बन्धी जानकारी तपाईंको सुविधाको लागि मात्र प्रदान गरिएको छ र अद्यावधिकहरूद्वारा हटाइएको हुन सक्छ। यो सुनिश्चित गर्न को लागी तपाइँको जिम्मेवारी हो कि तपाइँको आवेदन तपाइँको विशिष्टताहरु संग मिल्छ। अतिरिक्त समर्थनको लागि आफ्नो स्थानीय माइक्रोचिप बिक्री कार्यालयमा सम्पर्क गर्नुहोस् वा, मा अतिरिक्त समर्थन प्राप्त गर्नुहोस् https://www.microchip.com/en-us/support/design-help/client-supportservices.

यो जानकारी माइक्रोचिप "जस्तो छ" द्वारा प्रदान गरिएको हो। MICROCHIP ले कुनै पनि प्रकारको कुनै प्रतिनिधित्व वा वारेन्टी गर्दैन चाहे अभिव्यक्त होस् वा निहित, लिखित वा मौखिक, वैधानिक वा अन्यथा, जानकारीसँग सम्बन्धित होस्, तर गैर-सीमितता सहित, गैर-सीमितता सहितको जानकारीसँग सम्बन्धित। पोज, वा सम्बन्धित वारेन्टीहरू यसको अवस्था, गुणस्तर, वा प्रदर्शन। कुनै पनि हालतमा MICROCHIP कुनै पनि अप्रत्यक्ष, विशेष, दण्डात्मक, आकस्मिक, वा परिणामात्मक हानि, क्षति, लागत, वा कुनै पनि प्रकारको खर्चको लागि उत्तरदायी हुनेछैन। सम्भाव्यता वा क्षतिहरू अनुमानित छन्। कानूनद्वारा अनुमति दिइएको पूर्ण हदसम्म, जानकारी वा यसको प्रयोगसँग सम्बन्धित कुनै पनि हिसाबले सबै दावीहरूमा माइक्रोचिपको पूर्ण दायित्व, तपाईंले कुनै पनि रकममा कुनै पनि रकम लिएको खण्डमा शुल्कको रकमभन्दा बढी हुने छैन।

जीवन समर्थन र/वा सुरक्षा अनुप्रयोगहरूमा माइक्रोचिप यन्त्रहरूको प्रयोग पूर्ण रूपमा क्रेताको जोखिममा हुन्छ, र क्रेता कुनै पनि र सबै क्षतिहरू, दावीहरू, सूटहरू, वा त्यस्ता प्रयोगको परिणामस्वरूप खर्चहरूबाट हानिरहित माइक्रोचिपलाई रक्षा गर्न, क्षतिपूर्ति गर्न र होल्ड गर्न सहमत हुन्छन्। कुनै पनि माइक्रोचिप बौद्धिक सम्पदा अधिकार अन्तर्गत कुनै पनि इजाजतपत्र, अस्पष्ट वा अन्यथा, अन्यथा भनिएको छैन।

माइक्रोचिपको गुणस्तर व्यवस्थापन प्रणालीको बारेमा जानकारीको लागि, कृपया भ्रमण गर्नुहोस् www.microchip.com/quality.

ट्रेडमार्कहरू

माइक्रोचिपको नाम र लोगो, माइक्रोचिप लोगो, Adaptec, AnyRate, AVR, AVR लोगो, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KLEXLNC, केएलएनसीएल, माइक्रोचिप maXTouch, MediaLB, megaAVR, Microsemi, Microsemi लोगो, MOST, MOST लोगो, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 लोगो, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyST, SFNST, Logo , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, र XMEGA संयुक्त राज्य अमेरिका र अन्य देशहरूमा माइक्रोचिप टेक्नोलोजीको दर्ता ट्रेडमार्कहरू हुन्। AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, हाइपर स्पीड कन्ट्रोल, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus, Qureiet SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, र ZL संयुक्त राज्य अमेरिका मा माइक्रोचिप टेक्नोलोजी को दर्ता ट्रेडमार्क हो।

आसन्न कुञ्जी दमन, AKS, एनालग-फर-द-डिजिटल उमेर, कुनै पनि क्यापेसिटर, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompaniontoc, DAMPIEM CDERMIC, DAMPIEM ट्रोल नेट, Map. , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB प्रमाणित लोगो, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICKit, PICtail, PowerSmart, PureSmart, IQMatrix , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, USBSHARC, TSHARC VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, र ZENA संयुक्त राज्य अमेरिका र अन्य देशहरूमा माइक्रोचिप टेक्नोलोजीको ट्रेडमार्कहरू हुन्।

SQTP संयुक्त राज्य अमेरिका मा माइक्रोचिप टेक्नोलोजी को एक सेवा चिन्ह हो

Adaptec लोगो, फ्रिक्वेन्सी अन डिमान्ड, सिलिकन स्टोरेज टेक्नोलोजी, Symmcom, र ट्रस्टेड टाइम अन्य देशहरूमा माइक्रोचिप टेक्नोलोजी इन्कका दर्ता ट्रेडमार्क हुन्।

GestIC माइक्रोचिप टेक्नोलोजी जर्मनी II GmbH & Co. KG को दर्ता गरिएको ट्रेडमार्क हो, माइक्रोचिप टेक्नोलोजी इन्कको सहायक कम्पनी, अन्य देशहरूमा।

यहाँ उल्लेख गरिएका अन्य सबै ट्रेडमार्कहरू तिनीहरूको सम्बन्धित कम्पनीहरूको सम्पत्ति हुन्।

© 2009-2021, Microchip Technology Incorporated र यसका सहायक कम्पनीहरू।

सबै अधिकार सुरक्षित।

ISBN: 978-1-5224-9314-3

विश्वव्यापी बिक्री र सेवा

अमेरिका

- कर्पोरेट कार्यालय

2355 West Chandler Blvd।

Chandler, AZ 85224-6199

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९

प्राविधिक समर्थन: http://www.microchip.com/

समर्थन Web ठेगाना: www.microchip.com - एटलान्टा

डुलुथ, GA

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - अस्टिन, TX

टेलिफोन: ८००-५५५-०१९९ - बोस्टन

वेस्टबरो, एमए

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - शिकागो

Itasca, IL

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - डलास

एडिसन, TX

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - डेट्रोइट

नोभि, एमआई

टेलिफोन: ८००-५५५-०१९९ - ह्युस्टन, TX

टेलिफोन: ८००-५५५-०१९९ - इन्डियानापोलिस

Noblesville, IN

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९

टेलिफोन: ८००-५५५-०१९९ - लस एन्जलस

मिशन भिजो, CA

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९

टेलिफोन: ८००-५५५-०१९९ - Raleigh, NC

टेलिफोन: ८००-५५५-०१९९ - न्यूयोर्क, NY

टेलिफोन: ८००-५५५-०१९९ - सान जोस, CA

टेलिफोन: ८००-५५५-०१९९

टेलिफोन: ८००-५५५-०१९९ - क्यानडा - टोरन्टो

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९

एशिया/प्यासिफिक

- अस्ट्रेलिया - सिड्नी

टेलिफोन: १-८८८-४७२-५८५३ - चीन - बेइजिङ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - चेङ्दु

टेलिफोन: १-८८८-४७२-५८५३ - चीन - चोङकिङ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - डोंगगुआन

टेलिफोन: १-८८८-४७२-५८५३ - चीन - ग्वांगझाउ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - हांग्जाउ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - हङकङ SAR

टेलिफोन: ८००-५५५-०१९९ - चीन - नान्जिङ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - किंगदाओ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - सांघाई

टेलिफोन: १-८८८-४७२-५८५३ - चीन - शेनयाङ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - शेन्जेन

टेलिफोन: १-८८८-४७२-५८५३ - चीन - सुजाउ

टेलिफोन: १-८८८-४७२-५८५३ - चीन - वुहान

टेलिफोन: १-८८८-४७२-५८५३ - चीन - सियान

टेलिफोन: १-८८८-४७२-५८५३ - चीन - सियामेन

टेलिफोन: ८००-५५५-०१९९ - चीन - Zhuhai

टेलिफोन: ८००-५५५-०१९९ - भारत - बैंगलोर

टेलिफोन: १-८८८-४७२-५८५३ - भारत - नयाँ दिल्ली

टेलिफोन: १-८८८-४७२-५८५३ - भारत - पुणे

टेलिफोन: १-८८८-४७२-५८५३ - जापान - ओसाका

टेलिफोन: १-८८८-४७२-५८५३ - जापान - टोकियो

टेलिफोन: 81-3-6880- 3770 - कोरिया - डेगु

टेलिफोन: १-८८८-४७२-५८५३ - कोरिया - सियोल

टेलिफोन: १-८८८-४७२-५८५३ - मलेसिया - क्वालालम्पुर

टेलिफोन: १-८८८-४७२-५८५३ - मलेसिया - पेनाङ

टेलिफोन: १-८८८-४७२-५८५३ - फिलिपिन्स - मनिला

टेलिफोन: १-८८८-४७२-५८५३ - सिङ्गापुर

टेलिफोन: ८००-५५५-०१९९ - ताइवान - सिन चु

टेलिफोन: १-८८८-४७२-५८५३ - ताइवान - काओसिङ

टेलिफोन: १-८८८-४७२-५८५३ - ताइवान - ताइपेई

टेलिफोन: १-८८८-४७२-५८५३ - थाइल्याण्ड - बैंकक

टेलिफोन: १-८८८-४७२-५८५३ - भियतनाम - हो ची मिन्ह

टेलिफोन: १-८८८-४७२-५८५३

युरोप

- अस्ट्रिया - वेल्स

टेलिफोन: १-८८८-४७२-५८५३

फ्याक्स: १-८८८-४७२-५८५३ - डेनमार्क - कोपेनहेगन

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - फिनल्याण्ड - एस्पो

टेलिफोन: ६१-२-९८६८-६७३३ - फ्रान्स - पेरिस

टेलिफोन: 33-1-69-53-63-20

फ्याक्स: 33-1-69-30-90-79 - जर्मनी - Garching

टेलिफोन: ८००-५५५-०१९९ - जर्मनी - हान

टेलिफोन: ८००-५५५-०१९९ - जर्मनी - Heilbronn

टेलिफोन: ८००-५५५-०१९९ - जर्मनी - कार्ल्सरुहे

टेलिफोन: ८००-५५५-०१९९ - जर्मनी - म्युनिख

टेलिफोन: 49-89-627-144-0

फ्याक्स: 49-89-627-144-44 - जर्मनी - रोजेनहेम

टेलिफोन: १-८८८-४७२-५८५३ - इटाली - मिलान

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - इटाली - पाडोभा

टेलिफोन: ८००-५५५-०१९९ - नेदरल्याण्ड्स - ड्रुनेन

टेलिफोन: ८००-५५५-०१९९

फ्याक्स: ८००-५५५-०१९९ - नर्वे - ट्रोन्डहेम

टेलिफोन: ८००-५५५-०१९९ - पोल्याण्ड - वार्सा

टेलिफोन: ८००-५५५-०१९९ - रोमानिया - बुखारेस्ट

टेलिफोन: 40-21-407-87-50 - स्पेन - म्याड्रिड

टेलिफोन: 34-91-708-08-90

फ्याक्स: 34-91-708-08-91 - स्वीडेन - गोटेनबर्ग

टेलिफोन: 46-31-704-60-40 - स्वीडेन - स्टकहोम

टेलिफोन: १-८८८-४७२-५८५३ - UK - Wokingham

टेलिफोन: १-८८८-४७२-५८५३

फ्याक्स: १-८८८-४७२-५८५३

नोट:

यो पारिवारिक सन्दर्भ म्यानुअल खण्ड यन्त्र डेटा पानाहरूको पूरकको रूपमा सेवा गर्नको लागि हो। यन्त्र भेरियन्टमा निर्भर गर्दै, यो म्यानुअल खण्ड सबै dsPIC33/PIC24 उपकरणहरूमा लागू नहुन सक्छ। यो कागजातले तपाईंले प्रयोग गरिरहनुभएको यन्त्रलाई समर्थन गर्छ कि गर्दैन भनी जाँच्नको लागि कृपया हालको यन्त्र डेटा पानामा रहेको "फ्ल्याश कार्यक्रम मेमोरी" अध्यायको सुरुमा रहेको टिप्पणीलाई परामर्श गर्नुहोस्।

यन्त्र डेटा पानाहरू र पारिवारिक सन्दर्भ म्यानुअल खण्डहरू माइक्रोचिप विश्वव्यापीबाट डाउनलोड गर्नका लागि उपलब्ध छन् Webसाइट मा: http://www.microchip.com.

कागजातहरू / स्रोतहरू

|

माइक्रोचिप PIC24 फ्लैश प्रोग्रामिंग [pdf] प्रयोगकर्ता गाइड PIC24 फ्लैश प्रोग्रामिंग, PIC24, फ्ल्यास प्रोग्रामिंग, प्रोग्रामिंग |

|

माइक्रोचिप PIC24 फ्लैश प्रोग्रामिंग [pdf] प्रयोगकर्ता गाइड PIC24 फ्लैश प्रोग्रामिंग, PIC24, फ्ल्यास प्रोग्रामिंग |